Carbon nanorør -logisk enhed fungerer på subnanowatt -strøm

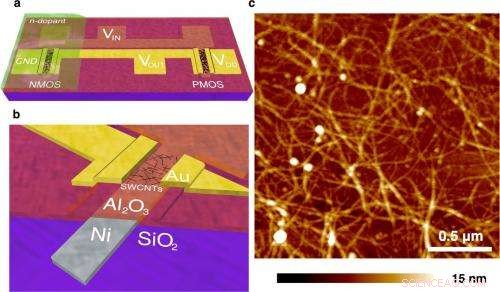

Illustrationer af (a) CNT CMOS-inverteren og (b) et tværsnit af en individuel CNT-transistor, inklusive en 25 nm tyk Ni-port, der muliggør ultralavt strømforbrug. (c) Atomkraftmikroskopibillede af CNT -filmmorfologien i transistorkanalområdet. Kredit:Geier, et al. ©2013 American Chemical Society

(Phys.org) —Forskere har demonstreret en ny carbon nanorør (CNT) -baseret logisk enhed, der kun bruger 0,1 nanowatt (nW) i sine statiske ON og OFF-tilstande, repræsenterer den laveste rapporterede værdi med 3 størrelsesordener for CNT-baserede CMOS-logikenheder. Enheden kan tjene som en byggesten til store områder, ultralaveffekt CNT logiske kredsløb, der kan bruges til at realisere en række forskellige nanoelektronikapplikationer.

Forskerne, Michael L. Geier, et al., ved Northwestern University i Evanston, Illinois, og University of Minnesota i Minneapolis, har offentliggjort deres papir om subnanowatt CNT -logikken i et nylig nummer af Nano bogstaver .

"Et moderne integreret kredsløb har mere end 1 milliard transistorer, " medforfatter Mark C. Hersam, Professor i materialevidenskab og teknik, Kemi, og medicin ved Northwestern University, fortalte Phys.org . "Følgelig, effekttab pr. transistor skal være meget lav, for at hele kredsløbet kan have et rimeligt strømforbrug. Faktisk, det er almindeligt accepteret, at strømforbrug er den vigtigste begrænsende faktor for at opnå yderligere stigninger i kompleksiteten (dvs. antal transistorer) i integrerede kredsløb. "

Som forskerne forklarer, en af de største fordele ved CMOS -arkitektur er, at den har et iboende lavt strømforbrug. Denne fordel stammer fra, at, i modsætning til andre logiske arkitekturer, en af de to typer transistorer (p-type eller n-type) er slukket under steady state-forhold i hver logisk gate i CMOS-enheder.

For fuldt ud at udnytte dette potentiale for ekstremt lavt strømforbrug, p-type og n-type transistorer skal have præcist indstillede og godt adskilte tærskelspændinger, som er spændingsniveauerne, der afgør, om enheden er ON eller OFF. Indtil nu, dette spørgsmål om tærskelspændingerne er ikke blevet behandlet, og forskerne her identificerede det som den centrale udfordring, der begrænser realiseringen af stærkt integreret CNT-baseret CMOS-elektronik.

I deres undersøgelse, forskerne brugte en metalgatestruktur til at opnå symmetriske og klart adskilte tærskelspændinger for p-type og n-type CNT-transistorer, hvilket resulterer i det ultralave strømforbrug. I de statiske tilstande, hvor enheden enten er ON eller OFF, strømforbruget er mindre end 0,1 nW. Ved midtpunktet af overførselstilstanden, når både p-type og n-type transistorer samtidigt er i ON-tilstand, spændingen når sit højdepunkt ved 10 nW.

Ved at forbinde flere CNT-transistorer i forskellige konfigurationer, forskerne viste inverter, NAND og NOR logiske porte. I fremtiden, disse porte kan integreres i komplekse kredsløb, hvor de kan levere subnanowatt statisk strømforbrug sammen med de andre fordele ved CNT'er, såsom løsningsprocesserbarhed og fleksibilitet.

"Vi arbejder nu på at lave mere komplicerede kredsløb, hvor vi vil have væsentligt flere transistorer og kaskadede logiske porte, "Sagde Hersam." Vi har også en interesse i at kombinere carbon nanorør med andre nye nanoelektroniske materialer i vores laboratorium (f.eks. molybdendisulfid [MoS 2 ])."

© 2013 Phys.org. Alle rettigheder forbeholdes.

Varme artikler

Varme artikler

-

Atomer bruger tunneler til at undslippe grafendækningKredit:Leiden Institut for Fysik Grafen har haft et stort potentiale for praktiske anvendelser, siden det først blev isoleret i 2004. Men vi bruger det stadig ikke i vores store teknologi, fordi v

Atomer bruger tunneler til at undslippe grafendækningKredit:Leiden Institut for Fysik Grafen har haft et stort potentiale for praktiske anvendelser, siden det først blev isoleret i 2004. Men vi bruger det stadig ikke i vores store teknologi, fordi v -

Ny forskning viser, at grafen kan fungere som overfladeaktivt stofKredit:CC0 Public Domain Ny forskning i grafenflager har opdaget, at materialet kan fungere som et overfladeaktivt stof, for første gang demonstrerer det, hvordan det kan være en alsidig 2-D stabi

Ny forskning viser, at grafen kan fungere som overfladeaktivt stofKredit:CC0 Public Domain Ny forskning i grafenflager har opdaget, at materialet kan fungere som et overfladeaktivt stof, for første gang demonstrerer det, hvordan det kan være en alsidig 2-D stabi -

Ingeniører viser, at lys kan spille vippe på nanoskalaKredit: Natur nanoteknologi (2014) doi:10.1038/nnano.2014.200 University of Minnesota elektriske ingeniørforskere har udviklet en unik enhed i nanoskala, der for første gang demonstrerer mekanisk

Ingeniører viser, at lys kan spille vippe på nanoskalaKredit: Natur nanoteknologi (2014) doi:10.1038/nnano.2014.200 University of Minnesota elektriske ingeniørforskere har udviklet en unik enhed i nanoskala, der for første gang demonstrerer mekanisk -

Træsvamp opsuger olie fra vandKredit:American Chemical Society Olieudslip og industriel udledning kan forurene vandet med fedtede stoffer. Selvom det er rigtigt, at olie og vand ikke blandes, at adskille og genvinde hver kompo

Træsvamp opsuger olie fra vandKredit:American Chemical Society Olieudslip og industriel udledning kan forurene vandet med fedtede stoffer. Selvom det er rigtigt, at olie og vand ikke blandes, at adskille og genvinde hver kompo

- CERN deler sig med videnskabsmand over stødende bemærkninger om kvinder

- Nøglen til at sænke kuldioxidemissionerne er lavet af metal

- Kina taler med European Space Agency om måneudpost

- Bugbid fra strandsand

- Amerikansk ekspert siger, at 5G -tiff kan påvirke informationsudveksling

- Molekylære nanocarboner med mekaniske bindinger