Selektiv drift af forbedrings- og udtømningstilstande for felteffekttransistorer i nanoskala

Transistorer i nanoskala er efterspurgte efter effektive digitale kredsløb, og forspænding af hver enhed er kritisk. Disse stringente forspændingsbetingelser kan lempes ved at opnå præcise værdier af transistorens tærskelspændinger. Dette fører til mere tolerante logiske tilstande for den elektriske støj.

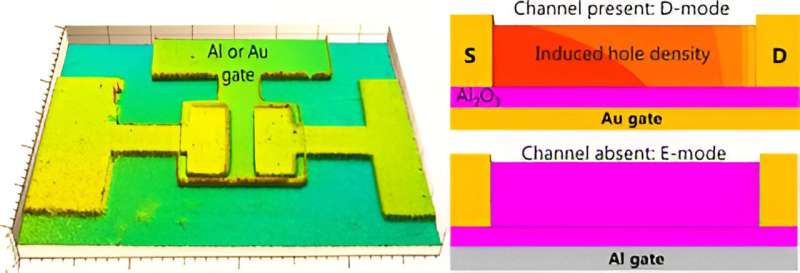

For at opfylde kravene til reduceret strømforbrug er CMOS-felteffekttransistorer (FET'er) fremstillet således, at de fungerer i forbedringstilstand (E), dvs. der er ingen frie ladningsbærere i kanalen ved nul gate-spænding. På den anden side har depletion (D)-mode transistorer højere strømme end forbedringstilstand på grund af rigelig ladningsbærertæthed.

I modsætning til skift af FET-applikationer er off-tilstand af FET for højfrekvente applikationer ikke et obligatorisk krav. Faktisk er tilstedeværelsen af en kanal ved nul gate forspænding fordelagtig for at opnå høj transkonduktans ved lavere spændinger. For Si FET'er blev forbedrings- eller udtømningstilstandene bestemt ved fremstillingstrinnet for ionimplantationsdoping. Det er dog udfordrende at implementere denne løsning til den nye generation af tynde materialer som organiske halvledere og 2D-materialer.

Ifølge ny forskning offentliggjort i ACS Applied Electronic Materials , ved at vælge en bestemt arbejdsfunktion for et gate-metal, kan tærskelspændinger af p-type FET'er ændres fra negative til positive værdier, hvilket er selektiv skift mellem forbedringstilstanden og udtømningstilstanden.

Forskerne fremstillede eksperimentelt FET'erne med forskellige gate-metalelektroder med forskellige arbejdsfunktioner. Tykkelsen af dielektrisk aluminiumoxid var kun 5 nm. På grund af denne korte adskillelse mellem gatemetallet og den organiske p-type halvledende kanal var der elektrostatisk interaktion mellem dem selv uden påføring af ekstern spænding. Når der bruges metal med lavt arbejde som aluminium (4,4 eV), fungerer FET'en i forbedringstilstand.

For højfunktions-gatemetaller som guld (5,0 eV) induceres et vist antal huller i kanalen ved nul gate-spænding. Dette fører til en god mængde strøm, som er kendt som udtømningstilstand.

For at bekræfte denne eksperimentelle observation udførte forskerne TCAD-enhedssimuleringer. Simuleringerne producerede farvekonturplot af induceret huldensitet. Den slags matchende eksperimentelle resultater og simuleringsresultater er meget vigtige fra et teknologisk synspunkt og storskalaproduktion.

Hovedforfatteren, Dr. Abhay Sagade fra SRMIST, Indien, afslørede, at de observerede effekter er dybe for tynde dielektriske tykkelser, såsom dem, der er mindre end 10 nm. For større tykkelser forbliver FET'erne i forbedringstilstand selv for gatemetaller med høje funktioner.

Dette koncept kan nemt udvides til alle tynde organiske, uorganiske og nye generationers 2D-materialer. Ved at bruge denne metode skulle det være muligt at fremstille mere kompakte, nøjagtige og rekonfigurerbare digitale logik- og oscillatorenheder og kredsløb. Yderligere kan D-mode OFET'er med forbedrede strømme udnyttes effektivt til højfrekvente applikationer.

Dette har også enorme implikationer for kommende kvanteenheder og teknologiske applikationer, der bruger små dimensionsfølsomme enheder.

Flere oplysninger: Abhay A. Sagade, Selektiv drift af forbedrings- og udtømningstilstande af nanoskala felteffekttransistorer, ACS-anvendte elektroniske materialer (2024). DOI:10.1021/acsaelm.3c01825

Leveret af SRM Institute of Science and Technology

Varme artikler

Varme artikler

-

Køling af træ:Ingeniører skaber stærke, bæredygtig løsning til passiv kølingForskere viser testapparatet til vurdering af kølevedets varmebevægelsesegenskaber. Kredit:University of Maryland Hvad hvis træet, dit hus var lavet af, kunne spare din elregning? I kapløbet om at

Køling af træ:Ingeniører skaber stærke, bæredygtig løsning til passiv kølingForskere viser testapparatet til vurdering af kølevedets varmebevægelsesegenskaber. Kredit:University of Maryland Hvad hvis træet, dit hus var lavet af, kunne spare din elregning? I kapløbet om at -

Ny undersøgelse præsenterer fordampningsdrevet transportkontrol af små molekyler langs nanospalte…Global, fordampningskontrolleret, mikro/nanofluid-anordning (GECMN) til transportkontrol af små molekyler. a) Skematisk illustration af GECMN bestående af to mikrokanaler forbundet til nanosliten. b)

Ny undersøgelse præsenterer fordampningsdrevet transportkontrol af små molekyler langs nanospalte…Global, fordampningskontrolleret, mikro/nanofluid-anordning (GECMN) til transportkontrol af små molekyler. a) Skematisk illustration af GECMN bestående af to mikrokanaler forbundet til nanosliten. b) -

Videnskabsmand opdager, hvordan bladfugle laver komplekse farveproducerende krystallerModhagespidser af hanlige blåvingede løvfugle, viser tilstedeværelsen af farveproducerende nanostrukturer. Kredit:Dr. Vinod Kumar Saranathan. En nylig undersøgelse foretaget af et team af forske

Videnskabsmand opdager, hvordan bladfugle laver komplekse farveproducerende krystallerModhagespidser af hanlige blåvingede løvfugle, viser tilstedeværelsen af farveproducerende nanostrukturer. Kredit:Dr. Vinod Kumar Saranathan. En nylig undersøgelse foretaget af et team af forske -

Forskere anvender en ny tilgang til at samle peptoider på en fast overfladeDette mikroskopibillede viser det todimensionelle netværk af hexagonalt mønstrede nanobånd dannet ved selvsamling af syntetiske proteinlignende polymerer (peptoider) på en mineraloverflade. Kredit:Pac

Forskere anvender en ny tilgang til at samle peptoider på en fast overfladeDette mikroskopibillede viser det todimensionelle netværk af hexagonalt mønstrede nanobånd dannet ved selvsamling af syntetiske proteinlignende polymerer (peptoider) på en mineraloverflade. Kredit:Pac

- Celler på et trangt sted

- Skattejæger finder 3, 000 år gammel skat i Skotland

- Forskere øger lysemissionen i 2D-halvledere med en faktor på 100

- NASA ser, at den tropiske depression, Pauls styrke, er forringet

- Satellit viser, at denne udspringer af en stor orkan for dig, Østlige Stillehav

- Sådan konverteres pris per kvadratmeter til pris per kvadratfod