Fremtiden for chips:SMART annoncerer en vellykket måde at fremstille nye integrerede silicium III-V-chips på

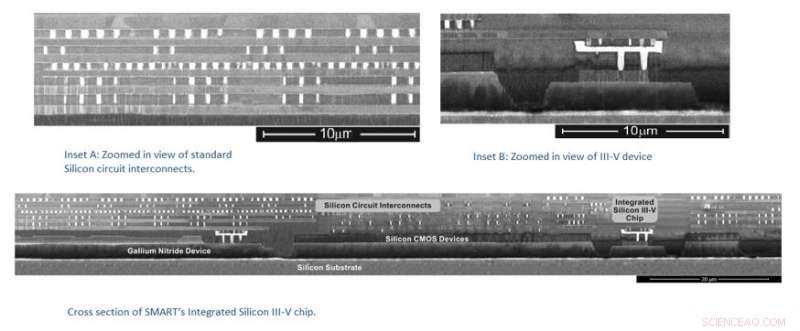

Tværsnit af SMARTs Integrated Silicon III-V-chip. Kredit:SMART

Singapore-MIT Alliance for Research and Technology (SMART), MIT's forskningsvirksomhed i Singapore, har annonceret den succesrige udvikling af en kommercielt levedygtig måde at fremstille integrerede Silicon III-V-chips med højtydende III-V-enheder indsat i deres design.

I de fleste enheder i dag, silicium-baserede CMOS-chips bruges til computere, men de er ikke effektive til belysning og kommunikation, hvilket resulterer i lav effektivitet og varmeudvikling. Dette er grunden til, at de nuværende 5G-mobilenheder på markedet bliver meget varme ved brug og vil lukke ned efter kort tid.

Det er her III-V halvledere er værdifulde. III-V chips er lavet af grundstoffer i 3. og 5. kolonne i det elementære periodiske system, såsom Gallium Nitride (GaN) og Indium Gallium Arsenide (InGaAs). På grund af deres unikke egenskaber, de er usædvanligt velegnede til optoelektronik (LED'er) og kommunikation (5G osv.) - hvilket øger effektiviteten betydeligt.

"Ved at integrere III-V i silicium, vi kan bygge på eksisterende produktionskapaciteter og billige volumenproduktionsteknikker af silicium og inkludere den unikke optiske og elektroniske funktionalitet af III-V teknologi, " sagde Eugene Fitzgerald, CEO og direktør, SMART, MIT's Research Enterprise i Singapore. "De nye chips vil være kernen i fremtidig produktinnovation og drive den næste generation af kommunikationsenheder, wearables og displays."

LEES-forsker gennemgår en 200 mm Silicon III-V wafer. Den innovative og kommercielle proces fra LEES udnytter eksisterende 200 mm halvlederproduktionsinfrastruktur til at skabe en ny generation af chips, der kombinerer traditionel silicium med III-V-enheder, noget, der ikke var kommercielt levedygtigt før Kredit:SMART

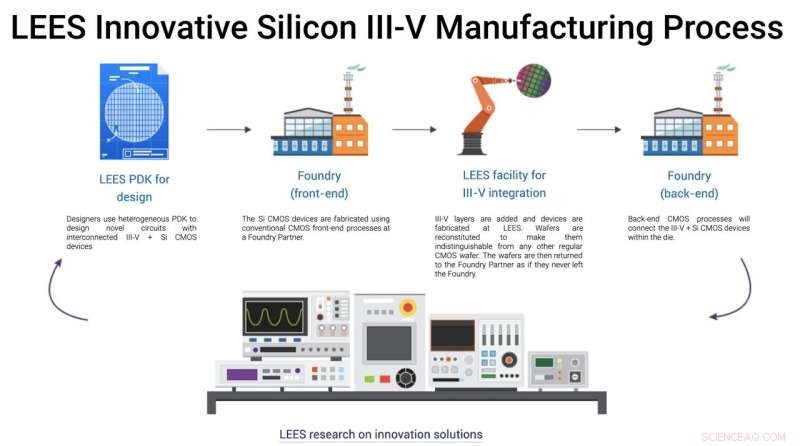

Kenneth Lee, Senior videnskabelig direktør for SMART LEES forskningsprogram tilføjer:"Men, at integrere III-V halvlederenheder med silicium på en kommercielt levedygtig måde er en af de sværeste udfordringer, som halvlederindustrien står over for, selvom sådanne integrerede kredsløb har været ønsket i årtier. Nuværende metoder er dyre og ineffektive, hvilket forsinker tilgængeligheden af de chips, som industrien har brug for. Med vores nye proces, vi kan udnytte eksisterende kapaciteter til at fremstille disse nye integrerede Silicon III-V-chips omkostningseffektivt og accelerere udviklingen og adoptionen af nye teknologier, der vil drive økonomier."

Den nye teknologi udviklet af SMART bygger to lag silicium og III-V enheder på separate substrater og integrerer dem lodret sammen inden for en mikron, hvilket er 1/50 af diameteren af et menneskehår. Processen kan bruge eksisterende 200 mm fremstillingsværktøjer, hvilket vil gøre det muligt for halvlederproducenter i Singapore og rundt om i verden at gøre ny brug af deres nuværende udstyr. I dag, omkostningerne ved at investere i en ny fremstillingsteknologi er i størrelsesordenen titusindvis af milliarder af dollars, Derfor er denne nye integrerede kredsløbsplatform yderst omkostningseffektiv og vil resultere i meget billigere nye kredsløb og elektroniske systemer.

SMART fokuserer på at skabe nye chips til pixeleret belysning/skærm og 5G-markeder, som har et samlet potentielt marked på over $100B USD. Andre markeder, som SMARTs nye integrerede Silicon III-V-chips vil forstyrre, omfatter bærbare mini-skærme, virtual reality-applikationer, og andre billedteknologier.

Hvordan LEES tilføjer værdi til din produktion. Kredit:SMART

Patentporteføljen er eksklusivt licenseret af New Silicon Corporation Pte. Ltd. (NSC), et Singapore-baseret spin-off fra SMART. NSC er den første fabelløse silicium-integrerede kredsløbsvirksomhed med proprietære materialer, processer, enheder, og design til monolitiske integrerede Silicon III-V kredsløb (www.new-silicon.com).

SMARTs nye integrerede Silicon III-V-chips vil være tilgængelige næste år og forventes i produkter i 2021.

Sidste artikelIngen, Alexa stopper ikke med at optage dig

Næste artikelHvad vil de næste 20 år rumme for kunstig intelligens?

Varme artikler

Varme artikler

-

I Houston, teknologi og sundhed er kure mod olieforbandelsenOlieinfrastrukturen i havnen i Houston tjener som en påmindelse om industriens betydning for den lokale økonomi I hjertet af Texas olieland, byen Houston kørte højt på oliebommen, men faldt så hår

I Houston, teknologi og sundhed er kure mod olieforbandelsenOlieinfrastrukturen i havnen i Houston tjener som en påmindelse om industriens betydning for den lokale økonomi I hjertet af Texas olieland, byen Houston kørte højt på oliebommen, men faldt så hår -

Ny high-definition satellitradar kan registrere broer med risiko for sammenbrud fra rummetMorandi -broen før dens kollaps. Ny satellitradarafbildning kan vise strukturenes bevægelse med millimeters nøjagtighed. Kredit: Fjernbetjening Forskere fra NASA Jet Propulsion Laboratory (JPL) o

Ny high-definition satellitradar kan registrere broer med risiko for sammenbrud fra rummetMorandi -broen før dens kollaps. Ny satellitradarafbildning kan vise strukturenes bevægelse med millimeters nøjagtighed. Kredit: Fjernbetjening Forskere fra NASA Jet Propulsion Laboratory (JPL) o -

Overførsel af måledata trådløst i realtidEn sensor overfører vibrationens spektre af blisken via 5G med sub -millisekund latens til en software. Kredit:Fraunhofer IPT Sensorer registrerer løbende målinger i anlæg og maskiner for at kontr

Overførsel af måledata trådløst i realtidEn sensor overfører vibrationens spektre af blisken via 5G med sub -millisekund latens til en software. Kredit:Fraunhofer IPT Sensorer registrerer løbende målinger i anlæg og maskiner for at kontr -

Ericsson, Swisscom lancerer Europas første store 5G -netværkEricsson og Swisscom har lanceret Europas første 5G -netværk Telekomudstyrsproducenten Ericsson sagde onsdag, at det havde lanceret det første europæiske store kommercielle 5G -netværk sammen med

Ericsson, Swisscom lancerer Europas første store 5G -netværkEricsson og Swisscom har lanceret Europas første 5G -netværk Telekomudstyrsproducenten Ericsson sagde onsdag, at det havde lanceret det første europæiske store kommercielle 5G -netværk sammen med