Demonstration af højhastigheds-SOT-MRAM-hukommelsescelle, der er kompatibel med 300 mm Si CMOS-teknologi

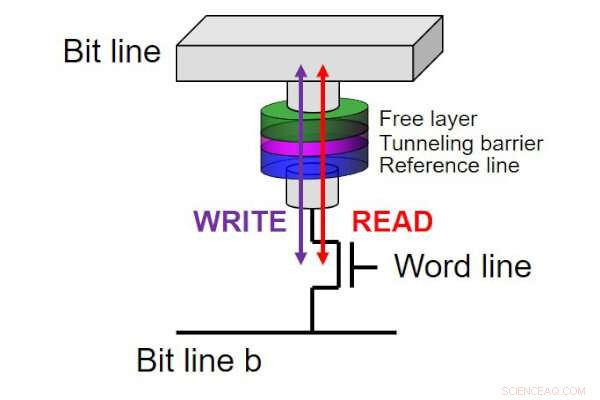

Skematisk af STT-MRAM-celle (to terminalenhed). Kredit:CIES, Tohoku Universitet

Forskere ved Tohoku University har annonceret demonstrationen af en højhastigheds spin-orbit-torque (SOT) magnetoresistiv random access memory celle kompatibel med 300 mm Si CMOS-teknologi.

Efterspørgslen efter laveffekt og højtydende integrerede kredsløb (IC'er) har været stigende, efterhånden som kunstig intelligens (AI) og Internet-of-Things (IoT) -enheder bliver mere udbredt. Med de nuværende IC'er, rent CMOS-baserede hukommelser såsom indlejret Flash-hukommelse (eFlash) og statisk random-access-hukommelse (SRAM) er ansvarlige for en høj andel af strømforbruget. For at sænke strømforbruget og samtidig bevare høj ydeevne, magnetoresistive random access memory (MRAM'er) er blevet intensivt udviklet. Spin-transfer torque MRAM'er (STT-MRAM'er) er de mest intensivt udviklede MRAM'er. Store halvledervirksomheder har nu annonceret, at de er klar til masseproduktion af STT-MRAM til eFlash-erstatning.

Forskere sigter mod at erstatte SRAM med MRAM. Til SRAM-udskiftning, MRAM skal opnå højhastighedsdrift over 500 MHz. For at imødekomme efterspørgslen, en alternativ MRAM, såkaldt spin-orbit torque MRAM (SOT-MRAM) blev foreslået, som har flere fordele ved højhastighedsdrift. På grund af disse fordele, SOT-MRAM er også blevet udviklet; imidlertid, de fleste laboratorieundersøgelser fokuserer på det grundlæggende i SOT-enheder. For at realisere SRAM-erstatning med SOT-MRAM, det er påkrævet at demonstrere højtydende SOT-MRAM-hukommelsescelle på et 300 mm CMOS-substrat. Ud over, det er nødvendigt at udvikle integrationsprocessen for SOT-MRAM, f.eks., termisk tolerance mod 400 ° C glødning, hvilket er et krav i standard CMOS back-end-of-line-processen.

-

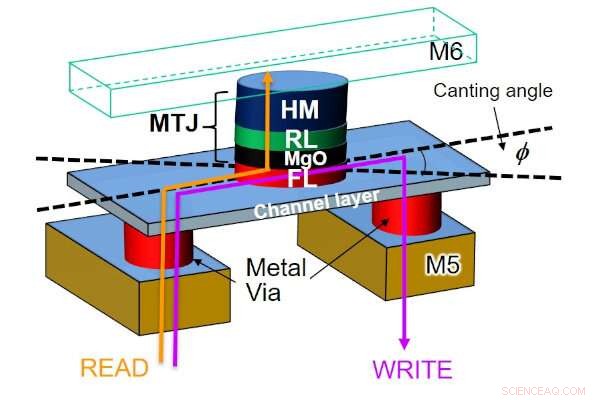

Et skematisk billede af SOT-MRAM-cellen (Three Terminal Device) Kredit:CIES, Tohoku Universitet

-

Et skematisk billede af den skråtstillede SOT-MRAM-celle. Kredit:CIES, Tohoku Universitet

Forskerholdet ledet af professorerne Tetsuo Endoh og Hideo Ohno - den nuværende præsident for Tohoku University - har udviklet en integrationsproces for SOT-enheder, der er kompatible med 55 nm CMOS-teknologi og fremstillede SOT-enheder på 300 mm CMOS-substrater. Den nyudviklede SOT-enhed har samtidig opnået højhastighedsskift ned til 0,35 ns og en tilstrækkelig høj termisk stabilitetsfaktor (E/k B T 70) til højhastigheds-ikke-flygtige hukommelsesapplikationer med robusthed mod udglødning ved 400 °C. Baseret på denne præstation, forskerholdet har integreret SOT-enheden med CMOS-transistorer og til sidst demonstreret højhastighedsdrift i komplette SOT-MRAM-hukommelsesceller.

Disse resultater har rettet problemerne med at gøre SOT-MRAM praktisk til kommercielle applikationer og dermed tilbyde en måde at erstatte SRAM med SOT-MRAM, som vil bidrage til realiseringen af højtydende elektronik med lavt strømforbrug.

Resultaterne vil blive præsenteret på 2019 IEEE International Electron Devices Meeting i San Francisco, 7-11 december, 2019.

Varme artikler

Varme artikler

-

Kooperativer for vedvarende energi, en mulighed for energiomstillingMøde om at inkorporere vedvarende energi-kooperativet Som Energia. Kredit:Som Energia Cooperativa Tre forskere fra UPV/EHUs ingeniørfakultet - Bilbao og University of Valladolid har undersøgt, hvo

Kooperativer for vedvarende energi, en mulighed for energiomstillingMøde om at inkorporere vedvarende energi-kooperativet Som Energia. Kredit:Som Energia Cooperativa Tre forskere fra UPV/EHUs ingeniørfakultet - Bilbao og University of Valladolid har undersøgt, hvo -

Baidu's omsætning i andet kvartal overgår forventningerne, men overskuddet falderBaidu-aktien steg 10 procent i efter-timers handel på New Yorks Nasdaq efter offentliggørelsen af resultaterne Den kinesiske internetgigant Baidu genvandt momentum i andet kvartal, med en bedre

Baidu's omsætning i andet kvartal overgår forventningerne, men overskuddet falderBaidu-aktien steg 10 procent i efter-timers handel på New Yorks Nasdaq efter offentliggørelsen af resultaterne Den kinesiske internetgigant Baidu genvandt momentum i andet kvartal, med en bedre -

Uber genaktiverer Colombia-tjenesten efter tre ugers pauseEn kvinde tjekker Ubers transportapplikation på sin mobiltelefon, efter at myndighederne har beordret dens suspension i Colombia, i Bogota den 20. december, 2019 Transportplatformen Uber genstarte

Uber genaktiverer Colombia-tjenesten efter tre ugers pauseEn kvinde tjekker Ubers transportapplikation på sin mobiltelefon, efter at myndighederne har beordret dens suspension i Colombia, i Bogota den 20. december, 2019 Transportplatformen Uber genstarte -

Comcast topper resultatprognoser; kabel-tv-abonnementer falderDenne 29. marts, 2017, filbillede viser et skilt uden for Comcast Center i Philadelphia. Comcast rapporterer om et stærkere overskud i andet kvartal end forventet, selvom det kæmper for at beholde kab

Comcast topper resultatprognoser; kabel-tv-abonnementer falderDenne 29. marts, 2017, filbillede viser et skilt uden for Comcast Center i Philadelphia. Comcast rapporterer om et stærkere overskud i andet kvartal end forventet, selvom det kæmper for at beholde kab

- Sådan konverteres fødder til Miles

- ESA hjælper med at analysere uberørte månesten

- Skinner lys over mørket af sod i luftforurening

- Fællesskabskarakteristika former klimaændringsdiskussioner efter ekstremt vejr

- Forskere indser sammenhængende lagring af lys over en time

- En ny strategi for naturlig produktbiosyntese