Dobbelte 8-bit gennembrud bringer AI til kanten

En chip, der omfatter flere PCM-enheder. De elektriske sonder, der kommer i kontakt med det, bruges til at sende signaler til individuelle enheder for at udføre multiplikationen i hukommelsen. Kredit:IBM

Denne uge, ved International Electron Devices Meeting (IEDM) og Conference on Neural Information Processing Systems (NeurIPS), IBM-forskere vil fremvise ny hardware, der vil bringe AI længere, end det har været før:lige til kanten. Vores nye tilgange til digitale og analoge AI-chips øger hastigheden og reducerer energibehovet til dyb læring, uden at ofre nøjagtigheden. På den digitale side, vi sætter scenen for en ny industristandard inden for AI-træning med en tilgang, der opnår fuld nøjagtighed med otte-bit præcision, accelererer træningstiden med to til fire gange i forhold til nutidens systemer. På den analoge side, vi rapporterer otte-bit præcision - den hidtil højeste - for en analog chip, nogenlunde en fordobling af nøjagtigheden sammenlignet med tidligere analoge chips, mens den bruger 33x mindre energi end en digital arkitektur med tilsvarende præcision. Disse præstationer varsler en ny æra af computerhardware designet til at frigøre AI's fulde potentiale.

Ind i post-GPU-æraen

Innovationer inden for software og AI-hardware har stort set drevet en forbedring på 2,5 gange om året i computerydelsen for AI siden 2009, da GPU'er først blev vedtaget for at accelerere dyb læring. Men vi er ved at nå grænserne for, hvad GPU'er og software kan. For at løse vores sværeste problemer, hardware skal opskaleres. Den kommende generation af AI-applikationer vil have brug for hurtigere responstider, større AI-arbejdsbelastninger, og multimodale data fra adskillige strømme. For at frigøre det fulde potentiale af AI, vi redesigner hardware med AI i tankerne:fra acceleratorer til specialbygget hardware til AI-arbejdsbelastninger, ligesom vores nye chips, og til sidst kvanteberegning til kunstig intelligens. Skalering af AI med nye hardwareløsninger er en del af en bredere indsats hos IBM Research for at flytte fra smal AI, bruges ofte til at løse specifikke, veldefinerede opgaver, til bred AI, som rækker ud på tværs af discipliner for at hjælpe mennesker med at løse vores mest presserende problemer.

Digitale AI-acceleratorer med reduceret præcision

IBM Research lancerede tilgangen med reduceret præcision til AI-modeltræning og inferens med et skelsættende papir, der beskriver en ny dataflow-tilgang til konventionelle CMOS-teknologier for at revidere hardwareplatforme ved dramatisk at reducere bitpræcisionen af data og beregninger. Modeller trænet med 16-bit præcision blev vist, for allerførste gang, at udvise intet tab af nøjagtighed i sammenligning med modeller trænet med 32-bit præcision. I de efterfølgende år, metoden med reduceret præcision blev hurtigt vedtaget som industristandard, med 16-bit træning og otte-bit inferencing nu almindeligt, og ansporede en eksplosion af nystartede virksomheder og venturekapital til reducerede præcisionsbaserede digitale AI-chips.

Den næste industristandard for AI-træning

Det næste store vartegn inden for træning med reduceret præcision vil blive præsenteret på NeurIPS i et papir med titlen "Training Deep Neural Networks with eight-bit Floating Point Numbers" (forfattere:Naigang Wang, Jungwook Choi, Daniel Brand, Chia-Yu Chen, Kailash Gopalakrishnan). I denne avis, en række nye ideer er blevet foreslået for at overvinde tidligere udfordringer (og ortodoksi) forbundet med at reducere træningspræcision under 16 bit. Ved at bruge disse nyligt foreslåede tilgange, vi har demonstreret, for første gang, evnen til at træne deep learning-modeller med otte-bit præcision, samtidig med at modellens nøjagtighed bevares på tværs af alle større AI-datasætkategorier:billede, tale, og tekst. Teknikkerne accelererer træningstiden for dybe neurale netværk (DNN'er) med to til fire gange i forhold til nutidens 16-bit systemer. Selvom det tidligere blev anset for umuligt at reducere præcisionen til træning yderligere, vi forventer, at denne otte-bit træningsplatform bliver en bredt udbredt industristandard i de kommende år.

Reduktion af bitpræcision er en strategi, der forventes at bidrage til mere effektive maskinlæringsplatforme i stor skala, og disse resultater markerer et væsentligt skridt fremad i skalering af AI. Ved at kombinere denne tilgang med en tilpasset dataflow-arkitektur, en enkelt chip-arkitektur kan bruges til effektivt at udføre træning og inferencing på tværs af en række arbejdsbelastninger og netværk, store som små. Denne tilgang kan også rumme "mini-batches" af data, kræves til kritiske brede AI-egenskaber uden at gå på kompromis med ydeevnen. At realisere alle disse egenskaber med otte-bit præcision til træning åbner også området for energieffektiv bred AI på kanten.

Analoge chips til in-memory computing

Takket være dets lave strømbehov, høj energieffektivitet, og høj pålidelighed, analog teknologi passer naturligt til AI på kanten. Analoge acceleratorer vil give næring til en køreplan for AI-hardwareacceleration ud over grænserne for konventionelle digitale tilgange. Imidlertid, der henviser til, at digital AI-hardware er i et kapløb om at reducere præcisionen, analog har hidtil været begrænset af dens relativt lave iboende præcision, påvirker modellens nøjagtighed. Vi udviklede en ny teknik til at kompensere for dette, opnå den højeste præcision til dato for en analog chip. Vores papir på IEDM, "8-bit Precision In-Memory Multiplication with Projected Phase-Change Memory" (forfattere:Iason Giannopoulos, Abu Sebastian, Manuel Le Gallo, V. P. Jonnalagadda, M. Sousa, M. N. Boon, Evangelos Eleftheriou), viser denne teknik opnået otte-bit præcision i en skalar multiplikationsoperation, en fordobling af nøjagtigheden af tidligere analoge chips, og forbrugte 33 gange mindre energi end en digital arkitektur med tilsvarende præcision.

Nøglen til at reducere energiforbruget er at ændre computerarkitekturen. Med nutidens computerhardware, data skal flyttes fra hukommelsen til processorer for at blive brugt i beregninger, hvilket tager meget tid og energi. Et alternativ er in-memory computing, i hvilke hukommelsesenheder måneskin som processorer, effektivt gør dobbelt pligt af både opbevaring og beregning. Dette undgår behovet for at flytte data mellem hukommelse og processor, sparer tid og reducerer energibehovet med 90 procent eller mere.

Faseændringshukommelse

Vores enhed bruger phase-change memory (PCM) til in-memory computing. PCM registrerer synaptiske vægte i dens fysiske tilstand langs en gradient mellem amorf og krystallinsk. Materialets ledningsevne ændres sammen med dets fysiske tilstand og kan modificeres ved hjælp af elektriske impulser. Sådan er PCM i stand til at udføre beregninger. Fordi tilstanden kan være hvor som helst langs kontinuummet mellem nul og én, det betragtes som en analog værdi, i modsætning til en digital værdi, som enten er et nul eller et, intet imellem.

Vi har forbedret præcisionen og stabiliteten af de PCM-lagrede vægte med en ny tilgang, kaldet projekteret PCM (Proj-PCM), hvor vi indsætter et ikke-isolerende projektionssegment parallelt med faseskiftesegmentet. Under skriveprocessen, projektionssegmentet har minimal indvirkning på enhedens drift. Imidlertid, under læsning, konduktansværdier for programmerede tilstande bestemmes for det meste af projektionssegmentet, som er bemærkelsesværdigt immun over for konduktansvariationer. Dette gør det muligt for Proj-PCM-enheder at opnå meget højere præcision end tidligere PCM-enheder.

Den forbedrede præcision opnået af vores forskerhold indikerer, at in-memory computing kan være i stand til at opnå højtydende dyb læring i miljøer med lav effekt, såsom IoT og edge-applikationer. Som med vores digitale acceleratorer, vores analoge chips er designet til at skalere til AI-træning og inferencing på tværs af visuelle, tale, og tekstdatasæt og strækker sig til nye brede AI. Vi vil demonstrere en tidligere offentliggjort PCM-chip hele ugen på NeurIPS, bruge det til at klassificere håndskrevne cifre i realtid via skyen.

Denne historie er genudgivet med tilladelse fra IBM Research. Læs den originale historie her.

Varme artikler

Varme artikler

-

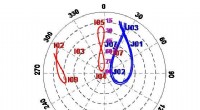

Ved du præcis, hvor du er?Skyplot af QZSS (blå) og IRNSS satellitter (rød) den 5. oktober, 2019 fra stationen CUT0 beliggende i Curtin University, Perth, Australien. Værdierne i sort er azimutvinklerne (i grader), og værdierne

Ved du præcis, hvor du er?Skyplot af QZSS (blå) og IRNSS satellitter (rød) den 5. oktober, 2019 fra stationen CUT0 beliggende i Curtin University, Perth, Australien. Værdierne i sort er azimutvinklerne (i grader), og værdierne -

Hårde nødder, knækket på en smart mådeAdditive Manufacturing gør det muligt at fremstille små metalstrukturer med en kompleks geometri. Her er et prøvestykke sammenlignet med et tændstikhoved. Brug af kunstig intelligens til at overvåge f

Hårde nødder, knækket på en smart mådeAdditive Manufacturing gør det muligt at fremstille små metalstrukturer med en kompleks geometri. Her er et prøvestykke sammenlignet med et tændstikhoved. Brug af kunstig intelligens til at overvåge f -

Seks regler for forbedring af bybustjenesterSmart busbrug kan transformere offentlig transport i byer, som EMBARQ gør i Brasilien. Kredit:EMBARQ Brasil/Flickr, CC BY-NC Offentlig transport, der er sikker, effektivt og effektivt er en kernep

Seks regler for forbedring af bybustjenesterSmart busbrug kan transformere offentlig transport i byer, som EMBARQ gør i Brasilien. Kredit:EMBARQ Brasil/Flickr, CC BY-NC Offentlig transport, der er sikker, effektivt og effektivt er en kernep -

Facebook suspenderer canadisk virksomhed på grund af en data mining-skandaleEt nyt kunstig intelligens-værktøj, der er skabt til at hjælpe med at identificere visse former for stofmisbrug baseret på en hjemløs ungdoms Facebook-opslag, kunne give hjemløse krisecentre vital inf

Facebook suspenderer canadisk virksomhed på grund af en data mining-skandaleEt nyt kunstig intelligens-værktøj, der er skabt til at hjælpe med at identificere visse former for stofmisbrug baseret på en hjemløs ungdoms Facebook-opslag, kunne give hjemløse krisecentre vital inf

- Ny kemisk metode baner vejen for at lave et større udvalg af lysfølsomme materialer

- Halogenbindingsmedieret metalfri kontrolleret kationisk polymerisation

- Projektet sigter mod at masseproducere nanoblade til sensorer, batterier

- Når ok ikke er ok:Sikkerhedspræsentant taler om syntetiske klik

- Hvordan planter og dyr interagerer i regnskoven

- Sådan beregnes hastighed fra temperatur