Innovation baner vejen for sensorgrænseflader, der er 30 gange mindre

NUS Green IC-teamet:Dr. Orazio Aiello (til venstre) og lektor Massimo Alioto (til højre). Kredit:National University of Singapore

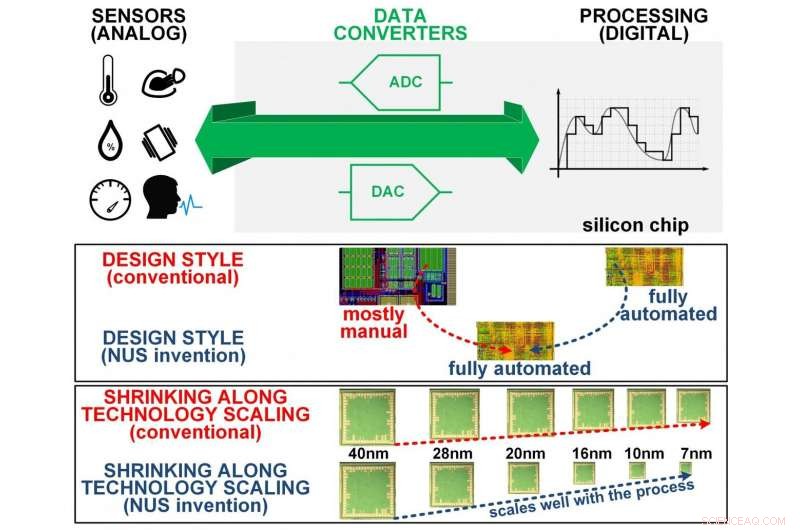

Den grønne IC-forskningsgruppe i Institut for Elektro- og Computerteknik ved National University of Singapores (NUS) Ingeniørfakultet opfandt en ny klasse af Digital-to-Analog (DAC) og Analog-to-Digital Converters (ADC), der kan være helt designet med en fuldautomatisk digital designmetodologi, takket være dens fuldt digitale arkitektur (fig. 1).

Sammenlignet med traditionelle analoge arkitekturer og metoder, designomløbstiden for disse nye sensorgrænseflader er reduceret fra måneder til timer. Den drastiske reduktion i designindsatsen er yderst fordelagtig i omkostningsfølsomme siliciumsystemer, såsom sensorer til tingenes internet (IoT). Den nye datakonverteringsarkitektur har også meget lav kompleksitet, reducere siliciumarealet og dermed produktionsomkostningerne med mindst 30 gange, sammenlignet med konventionelle designs.

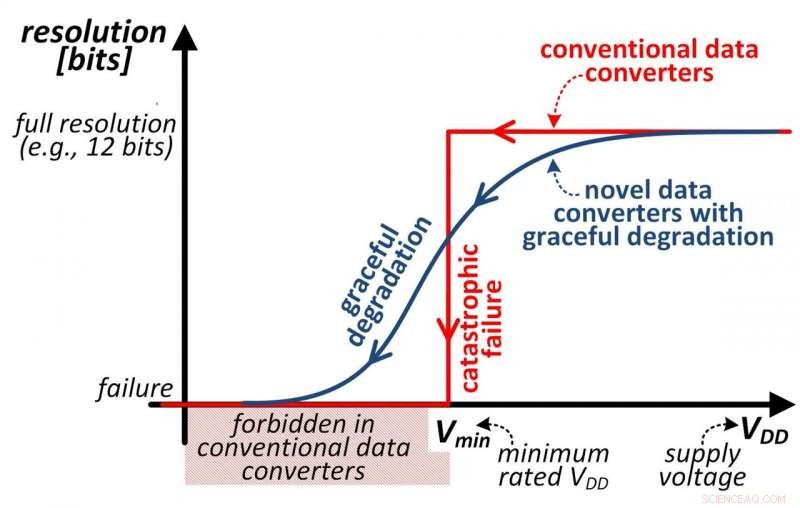

Sådanne nye datakonvertere udviser også den hidtil usete evne til elegant at forringe signaltroskaben, når dens forsyningsspænding eller klokfrekvens oplever store udsving (fig. 2). Sådanne udsving er almindelige i energihøstede IoT-sensorer, at strømmen høstet fra det omgivende miljø (f.eks. solcelle) er meget uregelmæssig. På tur, dette tillader uafbrudt sensorsignalovervågning selv under ugunstige høstede strømforhold, og uden spændingsregulering. I stedet, traditionelle datakonvertere lider af katastrofal opløsningsforringelse, når forsyningsspændingen er under dens minimale nominelle værdi Vmin (eller frekvensen overstiger dens maksimale nominelle værdi) som i fig. derfor brug for strømkrævende kredsløb til spændings- og frekvensregulering.

Forskningen er udført i samarbejde med lektor Paolo Crovetti fra Politecnico di Torino i Italien, og er støttet af Singapores undervisningsministerium og EU-kommissionen.

Mindre sensorgrænseflader, enklere og hurtigere at designe

"Vores forskning transformerer det traditionelt analoge og for det meste manuelle design af datakonvertere til fuldautomatisk digitalt design, at reducere siliciumområdet med en størrelsesorden og designtiden med to størrelsesordener, gør det muligt for halvledervirksomheder at være omkostningskonkurrencedygtige og samtidig nå ud til markederne hurtigere, " sagde teamlederen lektor Massimo Alioto, der er fra Institut for Elektro- og Computerteknik på Det Tekniske Fakultet NUS.

Katastrofal fiasko er erstattet af yndefuld opløsningsforringelse i den nye klasse af konventionelle datakonvertere opfundet af NUS-teamet. Dette gør det muligt drastisk at forenkle systemdesignet, undertrykke behovet for nøjagtig spændingsregulering. Kredit:National University of Singapore

Han tilføjede, "At være digital, vores sensorgrænseflader overføres ubesværet på tværs af produktionsteknologier og applikationer, og kan nedsænkes i digitale kredsløb for at undgå den traditionelle indsats, der kræves af deres integration på den samme siliciumchip." (Fig. 1).

NUS-teamet demonstrerede konceptet gennem adskillige siliciumchips, der implementerede både DAC'er og ADC'er med ekstremt lavt areal. Som et eksempel, en 12-bit DAC fremstillet i 40nm standard CMOS-teknologi er blevet demonstreret med et areal svarende til diameteren af en hårstrå. Dens iboende egnethed til teknologiskalering gør, at den krymper med ca. yderligere 32 gange, når den implementeres i den i øjeblikket fineste teknologi (7 nm).

På samme tid, NUS-opfindelsen har vist sig at muliggøre datakonvertere med høj opløsning (op til 16 bit), samtidig med at der opnås designsenkelhed og kompakthed.

Teammedlem Dr. Orazio Aiello, som er gæsteforsker ved instituttet, sagde, "Vores team har introduceret et nyt designparadigme, der skubber os tættere på den ultimative vision om billig, teknologiskalerbare og ultrakompakte IoT-enheder."

En hidtil uset robusthed giver yderligere fordele på systemniveau

NUS-innovationen forenkler yderligere integreret systemdesign, udnyttelse af den hidtil usete evne til at modstå meget betydelige spændings- og frekvensudsving, dermed slække på nøjagtighedskravene i spændings- og frekvensgenerering.

Katastrofal fiasko er erstattet af yndefuld opløsningsforringelse i den nye klasse af konventionelle datakonvertere opfundet af NUS-forskerne. Kredit:National University of Singapore

Ja, konventionelle datakonvertere, der arbejder ved en forsyningsspænding under dens mindste nominelle værdi (eller for høje klokfrekvens), oplever katastrofale fejl, og dermed undlader at udføre sin tilsigtede funktion (fig. 2). Tværtimod, de innovative datakonvertere, der er opfundet af NUS-teamet, udviser en yndefuld forringelse af opløsningen og signalfideliteten, når forsyningsspændingen eller clockfrekvensen overstiger det tilladte område. Som et eksempel, en DAC designet til 1 V blev demonstreret til at fungere korrekt ved halvdelen af denne spænding, mens dens opløsning kun forringes med 1 bit, når forsyningsspændingen reduceres med væsentlige 0,3V.

Advokatprofessor Alioto sagde, "Evnen til at have en yndefuld opløsningsforringelse under spændings- og frekvensoverskalering undertrykker behovet for komplekse kredsløbsløsninger, der nøjagtigt regulerer forsyningsspændingen og klokfrekvensen, der bruges af datakonvertere. Med andre ord, vores datakonvertere er nemmere at designe, og også forenkle det system, de er ansat i."

Næste skridt

Holdet arbejder i øjeblikket på et nyt paradigme, der gør traditionelt analoge og designintensive siliciumundersystemer til digitale standard cellebaserede designs, der understøttes af fuldautomatiske designflows, skubber grænsen for klassisk digitalt assisteret design. Dette forskningsstudie involverer flere grundlæggende delsystemer såsom forstærkere, oscillatorer, spændings- og strømreferencer, og mange andre.

Forskerholdet sigter mod at transformere den måde, integrerede systemer er designet på, muliggør ultrahurtig, ultrakompakt og teknologibærbart design af hele systemer.

Varme artikler

Varme artikler

-

Fake news-model i etapevis udgivelse, men to forskere fyrer op for replikeringKredit:CC0 Public Domain Ikke den mest trøstende nyhed i teknologiens verden:Laboratoriet for kunstig intelligens (OpenAI), som er medstiftet af Elon Musk, sagde, at dets software for let kunne ti

Fake news-model i etapevis udgivelse, men to forskere fyrer op for replikeringKredit:CC0 Public Domain Ikke den mest trøstende nyhed i teknologiens verden:Laboratoriet for kunstig intelligens (OpenAI), som er medstiftet af Elon Musk, sagde, at dets software for let kunne ti -

Microsoft vender tilbage med smartphone efter højprofilerede flopsMicrosofts administrerende direktør Satya Nadella, venstre, giver hånd med Chief Product Officer Panos Panay, der holder en Surface Duo ved et arrangement onsdag, 2. okt. 2019, i New York. (AP Photo/M

Microsoft vender tilbage med smartphone efter højprofilerede flopsMicrosofts administrerende direktør Satya Nadella, venstre, giver hånd med Chief Product Officer Panos Panay, der holder en Surface Duo ved et arrangement onsdag, 2. okt. 2019, i New York. (AP Photo/M -

Sløret ansigt nyheder anonymitet får en kunstig intelligens spinSimon Fraser University professor Steve DiPaola demonstrerer sin AI-metode til nyhedsrapportering anonymitet. Kredit:SFU Et forskerhold fra SFUs School of Interactive Arts and Technology (SIAT) ha

Sløret ansigt nyheder anonymitet får en kunstig intelligens spinSimon Fraser University professor Steve DiPaola demonstrerer sin AI-metode til nyhedsrapportering anonymitet. Kredit:SFU Et forskerhold fra SFUs School of Interactive Arts and Technology (SIAT) ha -

Twitter følger Facebook, der slår ned på folketællingens misinformationKredit:CC0 Public Domain Sociale medievirksomheden Twitter Inc. udvidede politikker beregnet til at beskytte valgintegriteten til den amerikanske folketælling tirsdag, siger, at det vil forbyde in

Twitter følger Facebook, der slår ned på folketællingens misinformationKredit:CC0 Public Domain Sociale medievirksomheden Twitter Inc. udvidede politikker beregnet til at beskytte valgintegriteten til den amerikanske folketælling tirsdag, siger, at det vil forbyde in

- Hjælper blinde med at navigere

- Intern vagthund siger, at EPA fejlforvalter giftige webstedsoprydninger

- Efterhånden som AI bevæger sig ind i indholdsskabelse, forskere sigter mod at bekæmpe dens skævh…

- Billede:Oversvømmelser langs Nueces-floden

- Hvordan fungerer luftpumper?

- Lavindkomstblokke i 92% af amerikanske bysamfund har mindre trædække og er varmere