Ny neuromorf chip til AI på kanten, til en lille brøkdel af energien og størrelsen af nutidens computerplatforme

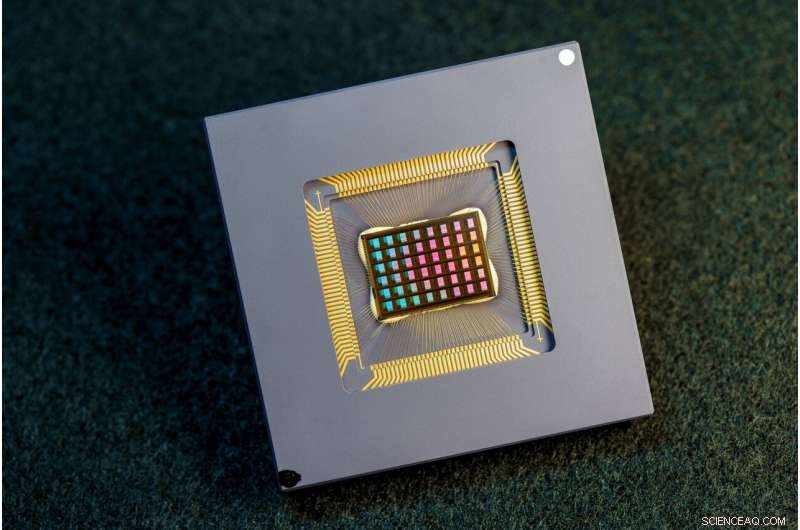

Et hold af internationale forskere designet, fremstillede og testede NeuRRAM-chippen. Kredit:David Baillot/University of California San Diego

Et internationalt team af forskere har designet og bygget en chip, der kører beregninger direkte i hukommelsen og kan køre en lang række forskellige AI-applikationer – alt sammen til en brøkdel af den energi, der forbruges af computerplatforme til generel AI-beregning.

NeuRRAM neuromorfe chip bringer AI et skridt tættere på at køre på en bred vifte af edge-enheder, adskilt fra skyen, hvor de kan udføre sofistikerede kognitive opgaver hvor som helst og når som helst uden at være afhængig af en netværksforbindelse til en centraliseret server. Applikationer findes i overflod i alle verdenshjørner og alle facetter af vores liv og spænder fra smarte ure til VR-headsets, smarte øretelefoner, smarte sensorer på fabrikker og rovere til rumudforskning.

NeuRRAM-chippen er ikke kun dobbelt så energieffektiv som de avancerede "compute-in-memory"-chips, en innovativ klasse af hybridchips, der kører beregninger i hukommelsen, den leverer også resultater, der er lige så nøjagtige som konventionelle digitale chips. Konventionelle AI-platforme er meget mere omfangsrige og er typisk begrænset til at bruge store dataservere, der opererer i skyen.

Derudover er NeuRRAM-chippen meget alsidig og understøtter mange forskellige neurale netværksmodeller og -arkitekturer. Som et resultat kan chippen bruges til mange forskellige applikationer, herunder billedgenkendelse og rekonstruktion samt stemmegenkendelse.

"Den konventionelle visdom er, at den højere effektivitet af compute-in-memory er på bekostning af alsidighed, men vores NeuRRAM-chip opnår effektivitet, mens den ikke ofrer alsidighed," sagde Weier Wan, papirets første tilsvarende forfatter og en nylig ph.d. uddannet fra Stanford University, som arbejdede på chippen, mens han var på UC San Diego, hvor han blev co-rådgivet af Gert Cauwenberghs i Institut for Bioteknik.

Forskerholdet, ledet af bioingeniører ved University of California San Diego, præsenterer deres resultater i udgaven af Nature den 17. august .

I øjeblikket er AI computing både strømkrævende og beregningsmæssigt dyrt. De fleste AI-applikationer på edge-enheder involverer flytning af data fra enhederne til skyen, hvor AI'en behandler og analyserer dem. Derefter flyttes resultaterne tilbage til enheden. Det skyldes, at de fleste edge-enheder er batteridrevne og som et resultat kun har en begrænset mængde strøm, der kan dedikeres til computere.

Ved at reducere strømforbruget, der er nødvendigt for AI-inferens på kanten, kan denne NeuRRAM-chip føre til mere robuste, smartere og tilgængelige kantenheder og smartere fremstilling. Det kan også føre til bedre databeskyttelse, da overførsel af data fra enheder til skyen kommer med øgede sikkerhedsrisici.

På AI-chips er flytning af data fra hukommelse til computerenheder en stor flaskehals.

"Det svarer til en otte-timers pendling for en to-timers arbejdsdag," sagde Wan.

For at løse dette dataoverførselsproblem brugte forskere, hvad der er kendt som resistiv hukommelse med tilfældig adgang, en type ikke-flygtig hukommelse, der giver mulighed for beregning direkte i hukommelsen i stedet for i separate computerenheder. RRAM og andre nye hukommelsesteknologier, der blev brugt som synapsearrays til neuromorfisk databehandling, blev udviklet i laboratoriet hos Philip Wong, Wans rådgiver hos Stanford og en hovedbidragyder til dette arbejde. Beregning med RRAM-chips er ikke nødvendigvis nyt, men generelt fører det til et fald i nøjagtigheden af de beregninger, der udføres på chippen, og en mangel på fleksibilitet i chippens arkitektur.

"Compute-in-memory har været almindelig praksis inden for neuromorfisk teknik, siden det blev introduceret for mere end 30 år siden," sagde Cauwenberghs. "Hvad der er nyt med NeuRRAM er, at den ekstreme effektivitet nu går sammen med stor fleksibilitet til forskellige AI-applikationer med næsten intet tab i nøjagtighed i forhold til standard digitale almene computerplatforme."

En omhyggeligt udformet metode var nøglen til arbejdet med flere niveauer af "samoptimering" på tværs af abstraktionslagene af hardware og software, fra design af chippen til dens konfiguration til at køre forskellige AI-opgaver. Derudover sørgede holdet for at tage højde for forskellige begrænsninger, der spænder fra hukommelsesenhedsfysik til kredsløb og netværksarkitektur.

"Denne chip giver os nu en platform til at løse disse problemer på tværs af stakken fra enheder og kredsløb til algoritmer," sagde Siddharth Joshi, en assisterende professor i datalogi og ingeniørvidenskab ved University of Notre Dame, som begyndte at arbejde på projektet som en ph.d. studerende og postdoktor i Cauwenberghs laboratorium ved UC San Diego.

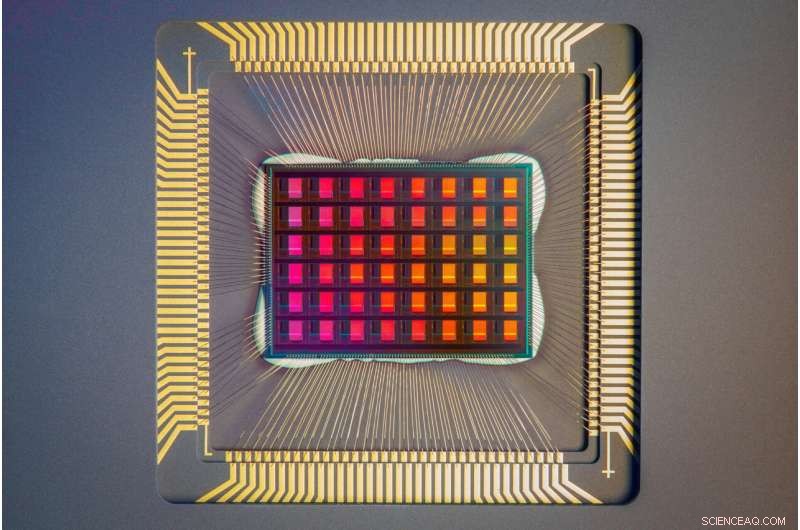

Et nærbillede af NeuRRAM-chippen. Kredit:David Baillot/University of California San Diego

Chip-ydeevne

Forskere målte chippens energieffektivitet ved et mål kendt som energiforsinkelsesprodukt eller EDP. EDP kombinerer både mængden af energi, der forbruges for hver operation, og mængden af gange, det tager at fuldføre operationen. Ved dette mål opnår NeuRRAM-chippen 1,6 til 2,3 gange lavere EDP (lavere er bedre) og 7 til 13 gange højere beregningstæthed end state-of-the-art chips.

Forskere kørte forskellige AI-opgaver på chippen. Det opnåede 99 % nøjagtighed på en håndskrevet ciffergenkendelsesopgave; 85,7 % på en billedklassificeringsopgave; og 84,7 % på en Google talekommando-genkendelsesopgave. Derudover opnåede chippen også en 70 % reduktion i billedgendannelsesfejl på en billedgendannelsesopgave. Disse resultater er sammenlignelige med eksisterende digitale chips, der udfører beregninger under samme bit-præcision, men med drastiske besparelser i energi.

Researchers point out that one key contribution of the paper is that all the results featured are obtained directly on the hardware. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

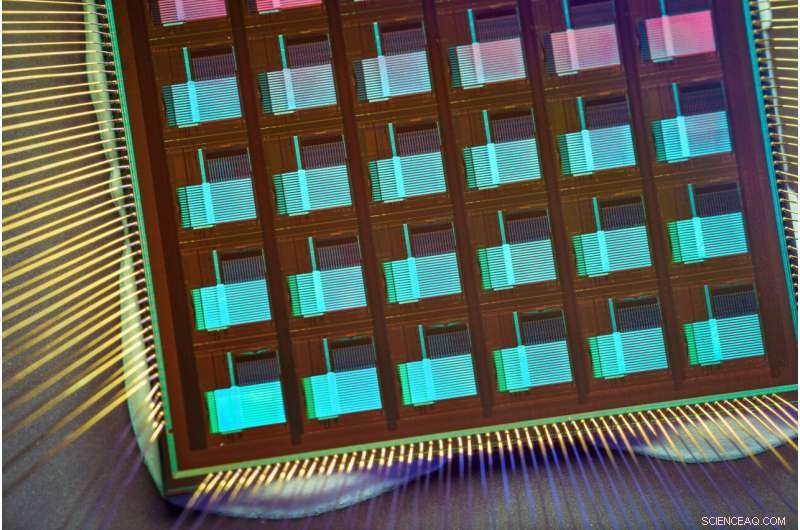

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. + Udforsk yderligere

A four-megabit nvCIM macro for edge AI devices

Varme artikler

Varme artikler

-

Apple -problemer rettes til FaceTime -aflytningsfejlApple siger, at det har rettet en softwarefejl, der kunne give brugerne mulighed for at se folk på FaceTime -applikationen, før de besvarede deres telefoner Apple sagde fredag, at det havde rettet

Apple -problemer rettes til FaceTime -aflytningsfejlApple siger, at det har rettet en softwarefejl, der kunne give brugerne mulighed for at se folk på FaceTime -applikationen, før de besvarede deres telefoner Apple sagde fredag, at det havde rettet -

Facebook, NYU går sammen om at gøre MR -scanninger hurtigere gennem AIKredit:CC0 Public Domain Facebook arbejder sammen med NYU School of Medicine for at forkorte den tid, patienterne skal bruge på MR -scannere. Facebooks gruppe for kunstig intelligens (FAIR) og læ

Facebook, NYU går sammen om at gøre MR -scanninger hurtigere gennem AIKredit:CC0 Public Domain Facebook arbejder sammen med NYU School of Medicine for at forkorte den tid, patienterne skal bruge på MR -scannere. Facebooks gruppe for kunstig intelligens (FAIR) og læ -

Forskere afmystificerer centralisering i cryptocurrency-minedriftIllustration af centralisering i Blockchain Mining. Flere store minepuljer dominerer processen. De resterende ressourcer er spredt blandt Oceanic Miners. Kredit:SUTD Blockchain-teknologi er blevet

Forskere afmystificerer centralisering i cryptocurrency-minedriftIllustration af centralisering i Blockchain Mining. Flere store minepuljer dominerer processen. De resterende ressourcer er spredt blandt Oceanic Miners. Kredit:SUTD Blockchain-teknologi er blevet -

CERN-facilitetens varme vil varme husholdninger i nabolandet Ferney-VoltaireGeotermiske prober implanteret i jorden under det nye område (de ni røde bundter på billedet) vil lagre varme, kompensere for temperatursvingninger i netværket. Kredit:Territoire d’Innovation Kan

CERN-facilitetens varme vil varme husholdninger i nabolandet Ferney-VoltaireGeotermiske prober implanteret i jorden under det nye område (de ni røde bundter på billedet) vil lagre varme, kompensere for temperatursvingninger i netværket. Kredit:Territoire d’Innovation Kan

- Stjerne til faldet idol:Carlos Ghosns japanske opgang og fald

- Mod ultrafølsomme diagnostiske chips

- Gør luftforurening dig syg? 4 spørgsmål besvaret

- Hvad kan polititrænere lære af den nuværende krise?

- En globalt vigtig mikrobiel proces skjult på marine partikler

- Europæisk rumfartsagentur skal hjælpe NASA med at tage mennesker ud over månen