Nye teknikker gør kulstofbaserede integrerede kredsløb mere praktiske

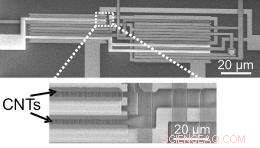

Et elektronmikroskopbillede, der viser carbon nanorør-transistorer (CNT'er) arrangeret i et integreret logisk kredsløb.

(PhysOrg.com) -- Stanfords ingeniører har bygget, hvad de mener er en chip med de mest avancerede computer- og lagerelementer lavet af kulstofnanorør til dato ved at udtænke en måde at udrydde den genstridige komplikation af nanorør, der forårsager kortslutninger.

Nanorør, som ligner mikroskopiske sugerør af sammenrullet kyllingetråd, betragtes bredt som den potentielle næste generation af materialer til at muliggøre forbedret hastighed og energieffektivitet af computerchips.

Forskerne præsenterede deres resultater i dag på International Electron Devices Meeting (IEDM) i Baltimore, sammen med endnu et fremskridt i at bruge nanorør til at lave flerlags, tredimensionelle kredsløb.

"Dette arbejde illustrerer, at kulstof-nanorør-transistorteknologi har bevæget sig ud over den videnskabelige opdagelses område og ind i ingeniørforskning, " sagde H.-S. Philip Wong, en professor i elektroteknik ved Stanford og medforfatter til papiret. "Vi er nu i stand til at konstruere enheder og bygge kredsløb på en wafer-skala i modsætning til tidligere 'one-of-a-kind' type demonstrationer. Enheder er i et kredsløbsmiljø, der er relevant for både nutidens og morgendagens systembehov."

Den håndfuld nanorørtransistorer i de kredsløb, som holdet fremstillede, kan ikke sammenlignes med de hundrede millioner transistorer på en kommerciel mikroprocessor eller hukommelseschip. men deres arrangement, den måde, de blev lavet på, og deres egenskaber er meget tættere på kommerciel kvalitet end nogen anden nanorør-enhed, der er lavet før, sagde Subhasish Mitra, en assisterende professor i datalogi og elektroteknik ved Stanford.

Transistorerne er grupperet i de samme "kaskadende" sekvenser, der er nødvendige for at producere beregningslogik og hukommelse, og den proces, der bruges til at fremstille dem, er kompatibel med den industrielle VLSI (very large scale integration) fremstillingsstandard.

"Vi er meget tilfredse med de hurtige fremskridt, der gøres af professorerne Wong og Mitra og deres forskerhold med at udvikle disse teknologier for at hjælpe med at overvinde barrierer for yderligere integration af komplekse kulstofbaserede elektroniske kredsløb, som vil føre til mere nyttige produkter til fremtidige generationer, " sagde Betsy Weitzman, Executive Vice President og direktør for Semiconductor Research Corporations Focus Center Research Program, som var med til at finansiere forskningen, sammen med National Science Foundation.

Chipsene anvender tre avancerede teknikker opfundet i Stanford for at overvinde endemiske problemer forbundet med nanorør. En, opfundet i 2007, giver transistorer mulighed for at arbejde, uanset om komponent-nanorørene ligger helt lige. En anden, opfundet i 2008, muliggør fremstilling i VLSI-skala af nanorørtransistorer på en chip. Den annoncerede i dag på IEDM, er en proces til pålideligt at fjerne nanorør, der altid leder elektrisk strøm, selv når de ikke skal. Sådanne besværlige "metalliske" nanorør kan kortslutte transistorer, hvis de ikke fjernes. Vanskeligheden for forskere er at finde måder at fjerne alle de besværlige nanorør, uden at beskadige nogen anden del af et kredsløb, herunder de nanorør, der opfører sig ordentligt.

Den nye teknik, som forskerne kalder VLSI-kompatibel Metallic Nanotube Removal (VMR), bygger på en idé, som først blev foreslået af Paul Collins og kolleger hos IBM i 2001. Ideen var at bryde nanorørene op ved at udsætte dem for stærk strøm. Stanford-teamet har nu gjort ideen praktisk på en VLSI-skala ved at skabe et gitter af elektroder, der zapper de uønskede nanorør væk. Det samme elektrodegitter kan derefter ætses for at producere et hvilket som helst kredsløbsdesign, herunder dem, der gør brug af de Stanford-udviklede teknikker nævnt ovenfor.

Hovedforfatteren på VMR-papiret, der blev præsenteret på IEDM, er elektroingeniør Stanford-studerende Nishant Patil. Andre forfattere inkluderer elektroingeniørstuderende Albert Lin, Jie Zhang og Hai Wei, og bachelorstuderende Kyle Anderson.

3-D nanorør kredsløb

Fem medlemmer af teamet (Wei, Patil, Lin, Wong og Mitra) fulgte straks op på VMR-papiret på IEDM med en anden præsentation, der beskrev det første flerlags carbon nanorør tredimensionelt integreret kredsløb.

Ligesom parkeringshuse i flere niveauer, tredimensionelle kredsløb giver mulighed for pakning af flere enheder - i dette tilfælde, transistorer - ind i et begrænset område. På chips, den tredje dimension kan også reducere længden af nogle sammenkoblede ledninger, reduktion af energibehovet til datatransmission. Mens ingeniører for nylig er begyndt at gøre fremskridt med at bygge tredimensionelle kredsløb ved at stable og forbinde lag lavet med konventionelle materialer, Stanford-værket viser, at det kan gøres med nanorør på en måde, der er integreret fra starten som et 3-D-design, hvilket giver en højere tæthed af forbindelser mellem lag.

Indikerer, at fremskridt kan være muligt med nanorør, Stanford-forskerne var i stand til at skabe en prototype af tre-lags chip med snesevis af nanorørtransistorer, der var forbundet i fungerende logiske porte ved hjælp af nanorør og metalledninger. Hvad gjorde bedriften mulig, Mitra sagde, var brugen af en relativt lav temperatur proces, som forskerne udviklede sidste år, hvor nanorør overføres fra en kvartswafer til en siliciumchip.

En tilbageværende udfordring er at øge antallet af nanorør, der kan mønstres korrekt på et givet område af en chip, for at give mulighed for at fremstille de millioner af transistorer, som moderne design kræver. Det er ikke en forhindring, som forskerne forventer at forlade.

Begge projekter blev støttet af Focus Center Research Program og National Science Foundation's Directorate for Computer and Information Science and Engineering (CISE).

"NSF og især CISE, er meget interesseret i at udforske spændende nye veje til at opnå fortsatte hardware-ydeevneforbedringer ud over grænserne for Moores lov, " sagde Sampath Kannan, en CISE divisionsdirektør hos National Science Foundation.

"Holdet ledet af professorerne Mitra og Wong, støttet af adskillige bevillinger fra CISE, er banebrydende forskning langs en af disse veje. Deres nye resultater om VLSI-skala teknik til at håndtere metalliske carbon nanorør til kredsløbsdesign og deres eksperimentelle demonstration af uperfektionsimmune VLSI-kompatible CNT kredsløb bringer os tættere på at gøre integrerede kredsløb ved hjælp af carbon nanorør til en praktisk realitet."

Leveret af Stanford University (nyheder:web)

Varme artikler

Varme artikler

-

Sol og regn beskriver, hvordan nanopartikler kan undslippe fra plastikbelægninger til miljøetNIST-forskere simulerer sol og regn for at afgøre, om vejrlig får polymerbelægninger til at frigive de nanopartikler, de indeholder, til miljøet. Til venstre, Li-Piin Sung placerer en kommercielt tilg

Sol og regn beskriver, hvordan nanopartikler kan undslippe fra plastikbelægninger til miljøetNIST-forskere simulerer sol og regn for at afgøre, om vejrlig får polymerbelægninger til at frigive de nanopartikler, de indeholder, til miljøet. Til venstre, Li-Piin Sung placerer en kommercielt tilg -

DNA-byggesten baner vejen for forbedret lægemiddelleveringLås-DNAet (rødt) af den lukkede nanopore binder til nøgle-DNAet (grønt) for at åbne kanalen. Kredit:Jonathan Burns et al. Natur nanoteknologi, DOI 10.1038/nnano.2015.279 DNA er blevet brugt som en

DNA-byggesten baner vejen for forbedret lægemiddelleveringLås-DNAet (rødt) af den lukkede nanopore binder til nøgle-DNAet (grønt) for at åbne kanalen. Kredit:Jonathan Burns et al. Natur nanoteknologi, DOI 10.1038/nnano.2015.279 DNA er blevet brugt som en -

Rynker giver varmen et stød i søjlegrafenVarmetransport gennem søjlegrafen kunne gøres hurtigere ved at manipulere samlingerne mellem ark af grafen og nanorørene, der forbinder dem, ifølge forskere fra Rice University. Kredit:Lei Tao/Rice Un

Rynker giver varmen et stød i søjlegrafenVarmetransport gennem søjlegrafen kunne gøres hurtigere ved at manipulere samlingerne mellem ark af grafen og nanorørene, der forbinder dem, ifølge forskere fra Rice University. Kredit:Lei Tao/Rice Un -

Stealth-cap teknologi til lysemitterende nanopartiklerNanopartikler i blodet:Stealth-hætten forhindrer blodkomponenter i at klæbe. Overfladen er tværbundet af UV-stråling (forstørret billedafsnit) og er derfor stabil i biologiske systemer. Kredit:HZDR/K.

Stealth-cap teknologi til lysemitterende nanopartiklerNanopartikler i blodet:Stealth-hætten forhindrer blodkomponenter i at klæbe. Overfladen er tværbundet af UV-stråling (forstørret billedafsnit) og er derfor stabil i biologiske systemer. Kredit:HZDR/K.

- Det første teleskop på et Cherenkov Telescope Array-sted får sin debut

- Donorincitamenter er ikke altid lig med mere velgørende gaver, undersøgelse finder

- Ny forskning kan revolutionere fleksibel elektronik, solceller

- Ny undersøgelse forklarer, hvorfor superledning finder sted i grafen

- Forskere viser, hvordan man laver sin egen supernova

- Turende strukturer i et menneskeskabt interface