IBM-forskere demonstrerer fremtiden for databehandling med grafen, racerbane og kulstof nanorør gennembrud

I dag til IEEE International Electron Devices Meeting, IBM-forskere afslørede adskillige udforskende forskningsgennembrud, der kan føre til store fremskridt med at levere dramatisk mindre, hurtigere og mere kraftfulde computerchips.

I mere end 50 år, computerprocessorer er steget i kraft og skrumpet i størrelse med en enorm hastighed. Imidlertid, Nutidens chipdesignere rammer fysiske begrænsninger med Moores lov, standse tempoet i produktinnovation fra skalering alene.

Med stort set alt elektronisk udstyr i dag bygget på komplementær-symmetri metal-oxid-halvleder (CMOS) teknologi, der er et presserende behov for nye materialer og kredsløbsarkitekturdesign, der er kompatible med denne ingeniørproces, da teknologiindustrien nærmer sig fysiske skalerbarhedsgrænser for siliciumtransistoren.

Efter år med vigtige fysikfremskridt, som tidligere kun er opnået i et laboratorium, IBM-forskere har med succes integreret udviklingen og anvendelsen af nye materialer og logiske arkitekturer på wafere med en diameter på 200 mm (otte tommer). Disse gennembrud kan potentielt give et nyt teknologisk grundlag for konvergens af databehandling, meddelelse, og forbrugerelektronik.

Racerbanehukommelse

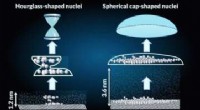

Racetrack-hukommelse kombinerer fordelene ved magnetiske harddiske og solid-state-hukommelse for at overvinde udfordringer med stigende hukommelseskrav og krympende enheder.

At bevise, at denne type hukommelse er mulig, I dag beskriver IBM-forskere den første Racetrack-hukommelsesenhed integreret med CMOS-teknologi på 200 mm wafers, kulminerende syv års fysikforskning.

Forskerne demonstrerede både læse- og skrivefunktionalitet på et array af 256 in-plane, magnetiserede vandrette racerbaner. Denne udvikling lægger grundlaget for yderligere at forbedre Racetrack-hukommelsens tæthed og pålidelighed ved hjælp af vinkelrette magnetiserede racerbaner og tredimensionelle arkitekturer.

Dette gennembrud kan føre til en ny type datacentreret databehandling, der gør det muligt at få adgang til enorme mængder af lagret information på mindre end en milliardtedel af et sekund.

Grafen

Denne første CMOS-kompatible grafenenhed nogensinde kan fremme trådløs kommunikation, og muliggør nye, højfrekvente enheder, som kan fungere under ugunstige temperatur- og strålingsforhold inden for områder som sikkerhed og medicinske applikationer.

Grafen integreret kredsløb, en frekvensmultiplikator, er operationel op til 5 GHz og stabil op til 200 grader Celcius. Mens detaljeret termisk stabilitet stadig skal evalueres, disse resultater er lovende for grafenkredsløb til brug i højtemperaturmiljøer.

Ny arkitektur vender den nuværende grafentransistorstruktur på hovedet. I stedet for at forsøge at afsætte gate-dielektrikum på en inert grafenoverflade, forskerne udviklede en ny indlejret gate-struktur, der muliggør højt enhedsudbytte på en 200 mm wafer.

Carbon nanorør

IBM-forskere demonstrerede i dag den første transistor med kanallængder på under 10 nm, udkonkurrerer de bedste konkurrerende siliciumbaserede enheder på disse længdeskalaer.

Selvom det allerede er overvejet i forskellige applikationer lige fra solceller til skærme, det forventes, at computere med i det næste årti vil bruge transistorer med en kanallængde under 10 nm, en længdeskala, hvor konventionel siliciumteknologi vil have ekstremt svært ved at præstere selv med nye avancerede enhedsarkitekturer. De skalerede carbon nanorør-enheder under 10nm gate-længde er et væsentligt gennembrud for fremtidige applikationer inden for computerteknologi.

Selvom det ofte er forbundet med at forbedre koblingshastigheden (on-state), dette gennembrud demonstrerer for første gang, at kulstof nanorør kan give fremragende off-state adfærd i ekstremt skalerede enheder - bedre end hvad nogle teoretiske estimater af tunnelstrøm foreslået.

Varme artikler

Varme artikler

-

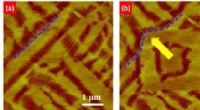

Erindringer om tidligere ting:Forskere opdager nanoskala formhukommelsesoxidDette AFM-billede viser en genvindelig fasetransformation i en vismutferritfilm introduceret af et påført elektrisk felt. Den stiplede blå linje viser flytningen af fasegrænserne. Kredit:Berkeley La

Erindringer om tidligere ting:Forskere opdager nanoskala formhukommelsesoxidDette AFM-billede viser en genvindelig fasetransformation i en vismutferritfilm introduceret af et påført elektrisk felt. Den stiplede blå linje viser flytningen af fasegrænserne. Kredit:Berkeley La -

Oxygen ledig stilling understøttet hukommelseProf. Dr. Lambert Alff (v.) og Sankaramangalam Ulhas Sharath. Kredit:Gabi Haindl En ikke-flygtig hukommelse, der holder sin digitale information uden strøm og arbejder på samme tid med den ultrahø

Oxygen ledig stilling understøttet hukommelseProf. Dr. Lambert Alff (v.) og Sankaramangalam Ulhas Sharath. Kredit:Gabi Haindl En ikke-flygtig hukommelse, der holder sin digitale information uden strøm og arbejder på samme tid med den ultrahø -

Forskerhold finder på at producere grafen med stort område 100 gange billigereDr. Ravinder Dahiya Grafen er blevet hyldet som et vidundermateriale, siden det først blev isoleret fra grafit i 2004. Grafen er kun et enkelt atom tykt, men det er fleksibelt, stærkere end stål,

Forskerhold finder på at producere grafen med stort område 100 gange billigereDr. Ravinder Dahiya Grafen er blevet hyldet som et vidundermateriale, siden det først blev isoleret fra grafit i 2004. Grafen er kun et enkelt atom tykt, men det er fleksibelt, stærkere end stål, -

Forsker udforsker kontaktfrysning af vand på nanoskalaKredit:Yale School of Engineering and Applied Science På nanoskala, vand fryser på forskellige måder, og ikke alle er helt forstået. Blandt andre fordele, at få bedre styr på disse processer kan b

Forsker udforsker kontaktfrysning af vand på nanoskalaKredit:Yale School of Engineering and Applied Science På nanoskala, vand fryser på forskellige måder, og ikke alle er helt forstået. Blandt andre fordele, at få bedre styr på disse processer kan b

- Forskere finder flere beviser for tsunamien fra det 14. århundrede, der udslettede Sumatran landsby…

- Månen er stadig geologisk aktiv, undersøgelse tyder på

- Opvarmning i Midtvesten kan resultere i majs, sojaproduktionen flytter nordpå

- Forskere observerer interferenseffekt mellem Floquet kvasipartikler ved hjælp af strontium optisk g…

- Sådan opbygges en Space Station Science Project

- Multitasking plasmoniske nanobubler dræber nogle celler, ændre andre