Tager transistorer ind i en ny dimension

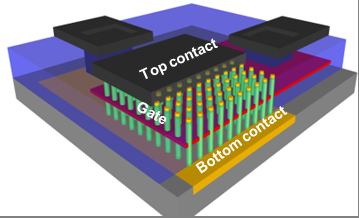

Diagram af en 3D nano-transistor, der viser porten (rød), der omgiver de lodrette nanotråde (grøn) og adskiller kontakterne i enderne af hver nanotråd (beige). Kredit:© X-L Han og G. Larrieu

Et nyt gennembrud kan skubbe grænserne for miniaturiseringen af elektroniske komponenter længere end hidtil antaget muligt. Et hold ved Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) og Institut d'Électronique, de Microélectronique et de Nanotechnologie (IEMN) har bygget en nanometrisk transistor, der viser exceptionelle egenskaber for en enhed af dens størrelse. For at opnå dette resultat, forskerne udviklede en ny tredimensionel arkitektur bestående af et vertikalt nanotrådsarray, hvis ledningsevne styres af en port, der kun måler 14 nm i længden.

Udgivet i Nanoskala , disse resultater åbner vejen mod alternativer til de plane strukturer, der anvendes i mikroprocessorer og hukommelsesenheder. Brugen af 3D-transistorer kan øge styrken af mikroelektroniske enheder markant.

Mikroelektronikkens "byggesten" transistorer består af en halvlederkomponent, kaldet kanal, forbinder to terminaler. Strømmen mellem disse terminaler styres af en tredje terminal, kaldet port. Fungerer som en kontakt, porten bestemmer, om transistoren er tændt eller slukket. I løbet af de sidste 50 år, transistorer er blevet støt reduceret i størrelse, muliggør udvikling af stadig stærkere mikroelektroniske enheder. Imidlertid, der er almindelig enighed om, at nutidens transistorer, med deres plane arkitektur, nærmer sig grænserne for miniaturisering:der er en minimumsstørrelse, hvorunder gatekontrollen over kanalen bliver mindre og mindre effektiv. I særdeleshed, lækstrømme begynder at forstyrre de logiske operationer udført af transistorarrayet. For at overvinde dette problem, forskere rundt om i verden undersøger alternativer, der vil gøre det muligt for kapløbet om miniaturisering at fortsætte.

Et team af forskere ved LAAS og IEMN har nu bygget den første virkelig tredimensionelle nanometriske transistor. Enheden består af et tæt lodret nanotrådsarray på omkring 200 nm i længden, der forbinder to ledende overflader. En kromport omgiver fuldstændig hver nanotråd og styrer strømmen, hvilket resulterer i optimal transistorstyring for et system af denne størrelse. Porten er kun 14 nm lang, sammenlignet med 28 nm for transistorerne i nutidens chips, men dens evne til at styre strømmen i transistorens kanal opfylder kravene til moderne mikroelektronik.

Denne arkitektur kan føre til udviklingen af mikroprocessorer, hvor transistorerne er stablet sammen. Antallet af transistorer i et givet rum kunne således øges betydeligt, sammen med ydeevnekapaciteten af mikroprocessorer og hukommelsesenheder. En anden væsentlig fordel ved disse komponenter er, at de er relativt enkle at fremstille og ikke kræver højopløsningslitografi. Ud over, disse 3D-transistorer kunne nemt integreres i de konventionelle mikroelektroniske enheder, der bruges af industrien i dag.

Der er indgivet patent på disse transistorer. Forskerne planlægger nu at fortsætte deres indsats for yderligere at reducere størrelsen af porten, som de mener kunne gøres mindre end 10 nm og samtidig give tilfredsstillende kontrol over transistoren. Ud over, teamet leder efter industrielle partnere til at hjælpe med at designe fremtidens elektroniske enheder ved hjælp af 3D-arkitekturen i disse nye transistorer.

Varme artikler

Varme artikler

-

Nanovidenskabens gennembrud:Undersøgelse af partikler mindre end en milliardtedel meterTinoxid-SNCer, der er fint fremstillet ved en dendrimer-skabelonmetode, sættes på de tynde silicaskallag af plasmoniske forstærkere, sådan at Raman-signalerne fra SNCerne er væsentligt forbedret til e

Nanovidenskabens gennembrud:Undersøgelse af partikler mindre end en milliardtedel meterTinoxid-SNCer, der er fint fremstillet ved en dendrimer-skabelonmetode, sættes på de tynde silicaskallag af plasmoniske forstærkere, sådan at Raman-signalerne fra SNCerne er væsentligt forbedret til e -

Nanopartikler, der bærer tre eller flere lægemidler, rummer potentiale for målrettet kræftbehand…Menneskelige kolorektale cancerceller. Kredit:NCI Center for Cancer Research Nanopartikler tilbyder en lovende måde at levere kræftmedicin på en målrettet måde, hjælper med at dræbe tumorer og skå

Nanopartikler, der bærer tre eller flere lægemidler, rummer potentiale for målrettet kræftbehand…Menneskelige kolorektale cancerceller. Kredit:NCI Center for Cancer Research Nanopartikler tilbyder en lovende måde at levere kræftmedicin på en målrettet måde, hjælper med at dræbe tumorer og skå -

Microcombing skaber stærkere, mere ledende carbon nanorørfilmKredit:Liwen Zhang Forskere fra North Carolina State University og Kinas Suzhou Institute of Nano-Science og Nano-Biotics har udviklet en billig teknik kaldet microcombing til at justere carbon na

Microcombing skaber stærkere, mere ledende carbon nanorørfilmKredit:Liwen Zhang Forskere fra North Carolina State University og Kinas Suzhou Institute of Nano-Science og Nano-Biotics har udviklet en billig teknik kaldet microcombing til at justere carbon na -

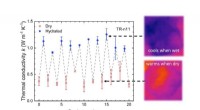

Termisk afbryder opdaget i konstruerede blækspruttebaserede biomaterialerGraf, der viser cyklusser af varmeledningsevne, når materialet er vådt og derefter tørt. Kredit:Melik Demirel, Penn State Tuning af materialer til optimale optiske og elektriske egenskaber er ved

Termisk afbryder opdaget i konstruerede blækspruttebaserede biomaterialerGraf, der viser cyklusser af varmeledningsevne, når materialet er vådt og derefter tørt. Kredit:Melik Demirel, Penn State Tuning af materialer til optimale optiske og elektriske egenskaber er ved

- MarCO giver plads til små opdagelsesrejsende

- Pizza mareridt:Kan din kost bestemme dine drømme?

- Video:Hvordan fungerer aircondition?

- Cement som klimamorder:Brug af industriaffald til at producere kulstofneutrale alternativer

- Ingeniører gør kritiske fremskridt inden for kvantecomputerdesign

- Samarbejde med jordmikrober, der er afgørende for plante- og dyreliv