Digital PLL opnår et strømforbrug på 0,265 mW

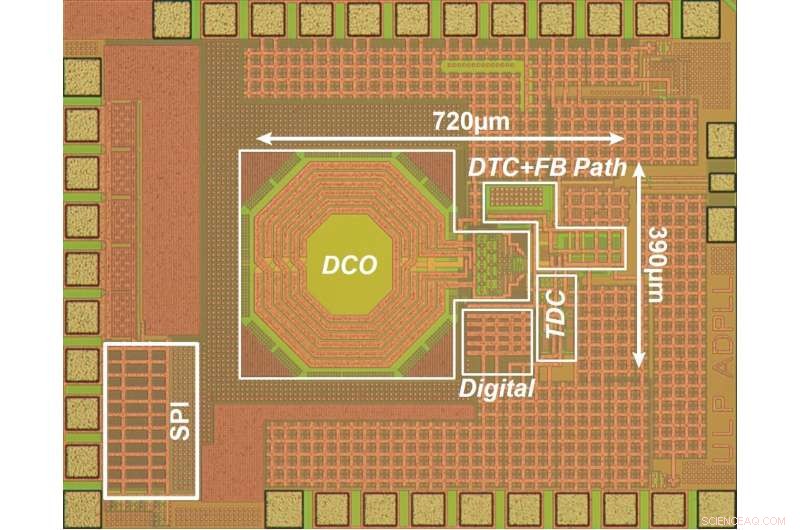

Den foreslåede fraktionerede-N DPLL fylder et område på 0,25 mm 2 i 65-nanometer CMOS. Kredit:Kenichi Okada

Forskere ved Tokyo Institute of Technology har udviklet en avanceret fase-låst sløjfe (PLL) frekvenssynthesizer, der drastisk kan reducere strømforbruget. Denne digitale PLL kan være en attraktiv byggesten for Bluetooth Low Energy (BLE) og andre trådløse teknologier til at understøtte en lang række Internet of Things (IoT) applikationer.

Som en vigtig byggesten for trådløse kommunikationssystemer, frekvenssynthesizere skal opfylde krævende krav. Selvom analoge PLL -frekvenssynthesizere har været standarden i mange år, ingeniører i IoT-industrien retter i stigende grad deres opmærksomhed mod såkaldte digitale PLL'er (DPLL'er) for at opnå ultra-lav effektdrift.

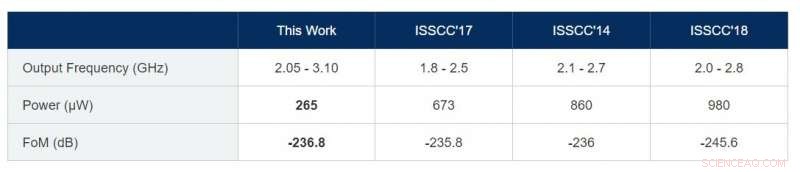

Kenichi Okada, lektor ved Tokyo Institute of Technology's Department of Electrical and Electronic Engineering og hans gruppe rapporterer nu en fraktioneret-N DPLL, der opnår et strømforbrug på kun 265 mikrowatt (μW), et tal, der er mindre end halvdelen af det laveste strømforbrug, der er opnået til dato (980 μW). (Tabel 1)

Forskerne fandt ud af, at det samlede strømforbrug kunne reduceres kraftigt ved hjælp af et automatisk feedback -kontrolsystem. "Denne automatisk skiftende feedbacksti bruger en effekt på 68 μW, hvilket fører til et strømforbrug på 265 μW for hele DPLL, "Siger Okada.

Den lovende DPLL kan fortsat bruges som en komponent til processorer, hukommelser og et stort nyt sortiment af IoT-enheder, der forventes at være både omkostningseffektive og miljøvenlige ved at køre på ultralav strøm. Okada bemærker, at tidlige forsøg viser, at DPLL kan forlænge batteriets levetid med fire gange.

Forskere ved Tokyo Institute of Technology har udviklet en avanceret fase-låst sløjfe (PLL) frekvenssynthesizer, der drastisk kan reducere strømforbruget. Denne digitale PLL kan være en attraktiv byggesten for Bluetooth Low Energy (BLE) og andre trådløse teknologier til at understøtte en lang række Internet of Things (IoT) applikationer. Kredit:Kenichi Okada

Dette papir er delvist baseret på resultater opnået fra et projekt bestilt af New Energy and Industrial Technology Development Organization (NEDO).

Dette arbejde præsenteres i Frequency Synthesizers-sessionen på den internationale Solid-State Circuits Conference (ISSCC) i 2019, verdens førende årlige forum om solid-state kredsløb og systemer-på-en-chip.

Varme artikler

Varme artikler

-

Hvor meget energi har vi egentlig brug for?Kredit:CC0 Public Domain To grundlæggende mål for menneskeheden er at udrydde fattigdom og reducere klimaændringer, og det er afgørende, at verden ved, om opnåelse af disse mål vil involvere afvej

Hvor meget energi har vi egentlig brug for?Kredit:CC0 Public Domain To grundlæggende mål for menneskeheden er at udrydde fattigdom og reducere klimaændringer, og det er afgørende, at verden ved, om opnåelse af disse mål vil involvere afvej -

Nintendo forbereder ny Switch -model, da salget er langsomtMens Nintendos Switch har vist sig at være populær, salget af gadgeten halter af Nintendo udvikler angiveligt en mindre, billigere version af sin populære Switch -spilkonsol, da salget af enheden

Nintendo forbereder ny Switch -model, da salget er langsomtMens Nintendos Switch har vist sig at være populær, salget af gadgeten halter af Nintendo udvikler angiveligt en mindre, billigere version af sin populære Switch -spilkonsol, da salget af enheden -

Google -arbejderoprør mod militærprojekt vokserOmkring et dusin Google -arbejdere siges at forlade virksomheden på grund af sit samarbejde med det amerikanske militær om droner Et internt andragende, der opfordrede Google til at holde sig væk

Google -arbejderoprør mod militærprojekt vokserOmkring et dusin Google -arbejdere siges at forlade virksomheden på grund af sit samarbejde med det amerikanske militær om droner Et internt andragende, der opfordrede Google til at holde sig væk -

Den britiske regulator forbyder Ryanairs vildledende grønne reklamerRyanair fastholder, at det er det grønneste flyselskab i Europa En britisk tilsynsmyndighed forbød onsdag annoncer fra Ryanair, der gav vildledende påstande om det irske flyselskabs lave niveau af

Den britiske regulator forbyder Ryanairs vildledende grønne reklamerRyanair fastholder, at det er det grønneste flyselskab i Europa En britisk tilsynsmyndighed forbød onsdag annoncer fra Ryanair, der gav vildledende påstande om det irske flyselskabs lave niveau af

- Rekordstor britisk nedbør i vinteren 2013-14 forårsaget af troperne, stratosfæren og klimaopvarmn…

- Hovedinstrument til NASAs WFIRST-mission fuldender milepælsgennemgang

- Betydningen af Flies

- Hvordan forurening påvirker mennesker

- Kæledyrskirkegårde afslører stigningen i troen på kæledyrs efterliv

- Er solenergi teknologien accepteret i dag?