En ny designstrategi til fremstilling af 2-D elektroniske enheder ved hjælp af ultratynde dielektrika

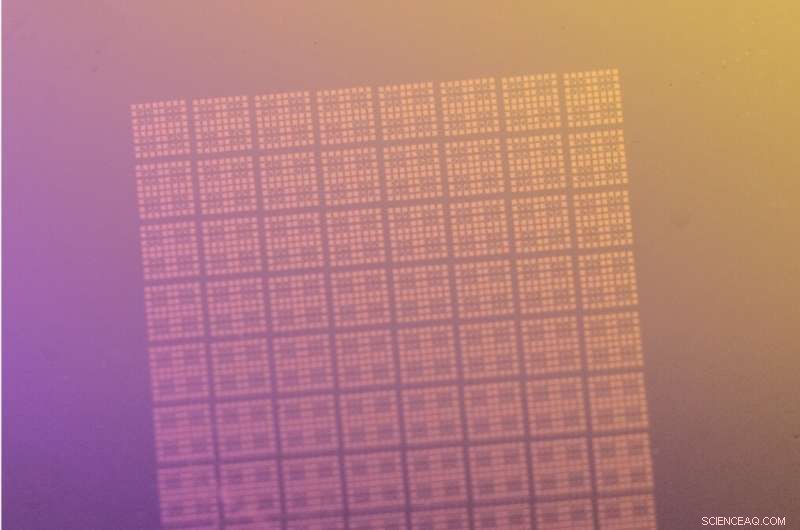

Billede af en enhedsarray fremstillet ved hjælp af metoden foreslået af forskerne. Kredit:Li et al.

2-D halvledere kan have meget nyttige applikationer, især som kanalmaterialer til laveffekttransistorer. Disse materialer udviser meget høj mobilitet ved ekstreme tykkelser, hvilket gør dem særligt lovende alternativer til silicium i fremstillingen af elektronik.

På trods af deres fordele, at implementere disse materialer i transistorer har indtil videre vist sig at være udfordrende. Faktisk, 2-D halvledere er af en dinglende-bindingsfri karakter; dermed, det er notorisk vanskeligt at deponere ultratynde høj-κ gate dielektrikum (dvs. stoffer med dielektriske egenskaber eller isolatorer) på materialerne via atomlagsdeposition (ALD), ofte resulterer i diskontinuerlige film.

Forskere ved Nanjing Universitet i Kina har for nylig præsenteret en ny strategi for at overvinde denne begrænsning, i sidste ende muliggør afsætning af gate-dielektrik på 2-D halvledere. I et papir udgivet i Naturelektronik , de rapporterede den vellykkede ALD af høj-k gate dielektrikum på 2-D halvledere ved hjælp af en molekylær krystal som et podningslag.

"Vores forskning forsøger at løse spørgsmålet om højkvalitets gate dielektrisk integration til 2-D transistorer, "Xinran Wang, en af de forskere, der har udført undersøgelsen, fortalte TechXplore. "I state-of-the-art Si-transistorer, den effektive oxidtykkelse (EOT) er blevet nedskaleret til under 1 nm. På nuværende tidspunkt, der er et stort hul mellem 2-D materialer og Si med hensyn til EOT, tæthed af grænsefladetilstand (Dit), og portlækage. Hvis man seriøst ønsker at skubbe 2-D transistorteknologi fremad, denne kløft skal overvindes."

Den fremgangsmåde, der blev introduceret af Wang og hans kolleger, muliggør produktion af dielektrikum med en ækvivalent oxidtykkelse på 1 nm på grafen, molybdændisulfid (MoS 2 ) og wolframdiselenid (WSe 2 ). De dielektrika, der er resultatet af forskernes tilgang, udviser en reduceret ruhed, tæthed af grænsefladetilstande og lækage sammenlignet med dem, der er produceret ved hjælp af mere konventionelle metoder. Interessant nok, de præsenterer også et forbedret opdelingsfelt.

"Andre end 2-D transistorer, en anden retning udforsket af min forskergruppe er organisk elektronik, "Tilføjede Wang." I løbet af de sidste mange år har vi har udviklet midler til præcist at kontrollere samlingen af molekyler på 2-D materialeoverfladen. For mange molekyler, herunder PTCDA, vi beviste, at vi kan kontrollere væksten så godt, at kun et monolag (~0,3 nm) er ensartet aflejret, med en meget ren grænseflade."

Interfacelaget oprettet af Wang og hans forskerhold i deres tidligere arbejde er et af de tyndeste grænsefladelag, der i øjeblikket kan opnås. I deres nuværende undersøgelse, de brugte dette lag til at fremstille grafen radiofrekvenstransistorer, der opererer ved 60 GHz, samt MoS 2 og WSe 2 komplementære metal-oxid-halvledertransistorer med en forsyningsspænding på 0,8 V og et lavt undertærskeludsving på 60 mV dec. -1 . Endelig, de brugte også deres teknik til at oprette MoS 2 transistorer med en kanallængde på 20 nm med et on/off-forhold på over 10 7 .

"Jeg tror, vores mest meningsfulde resultat var, at vi var i stand til at opnå 1 nm EOT i 2-D materialer, "Wang sagde." Det er en udbredt opfattelse, at 2-D-kanal kan reducere strømforbruget til transistorer sammenlignet med bulk-halvledere. Imidlertid, for at opnå det, vi skal bruge den samme driftsspænding, og transistorer kan slukkes skarpt (svingning under tærskelværdi tæt på 60 mV/dec). Begge mængder afhænger i høj grad af kvaliteten og tykkelsen af portdielektrikum. Vores undersøgelse demonstrerer i sandhed potentialet af 2-D-halvledere i retning af elektronik med lav effekt."

Wang og hans forskningsgruppe var de første til med succes at udvikle 2-D-transistorer med en 1 nm EOT, med succes at afsætte dielektrikum på tre forskellige materialer. Bemærkelsesværdigt, den EOT og gate lækage, de opnåede, er sammenlignelig med dem, der observeres i avanceret silicium CMOS, hvilket er et vigtigt skridt fremad på dette forskningsområde.

"Jeg tror, at der stadig er meget plads til forbedringer, " sagde Wang. "F.eks. Dit i 2-D-transistorer er stadig ~ 2 størrelsesordener højere end Si CMOS. Ud over, det ville være fantastisk at reducere EOT yderligere til ~0.8nm ved at bruge højere k-oxider. Endelig, kompatibiliteten af de materialer, vi udviklede med eksisterende CMOS-processer, mangler også at blive undersøgt."

© 2020 Science X Network

Sidste artikelForberedelse til brintøkonomien

Næste artikelFacebooks Zuckerberg ser langt på nytårsforsætter

Varme artikler

Varme artikler

-

Amerikanske teknologigiganter splittes om selskabsskat for at hjælpe hjemløseSan Franciscos hjemløseproblem er blevet forværret af det teknologiske boom, der pressede boligpriserne til himmels At beskatte San Franciscos rigeste virksomheder for at tøjle byens hjemløshedspr

Amerikanske teknologigiganter splittes om selskabsskat for at hjælpe hjemløseSan Franciscos hjemløseproblem er blevet forværret af det teknologiske boom, der pressede boligpriserne til himmels At beskatte San Franciscos rigeste virksomheder for at tøjle byens hjemløshedspr -

Det seneste:Aston Martin kombinerer luksus og elektrisk kraftDen nye Ferrari 488 Pista præsenteres under pressedagen på den 88. Geneve International Motor Show i Genève, Schweiz, Tirsdag, Marts 6, 2018. Motorudstillingen åbner sine porte for offentligheden fra

Det seneste:Aston Martin kombinerer luksus og elektrisk kraftDen nye Ferrari 488 Pista præsenteres under pressedagen på den 88. Geneve International Motor Show i Genève, Schweiz, Tirsdag, Marts 6, 2018. Motorudstillingen åbner sine porte for offentligheden fra -

Lavteknologisk, billige løsninger til forbedring af vandkvalitetenBarkdoll og Alizadeh Fard ser vand cirkulere i en eksperimentel vandtank udstyret med deres lavteknologiske, overkommelig intern rørmetode. Kredit:Michigan Technological University Dygtig, grundlæ

Lavteknologisk, billige løsninger til forbedring af vandkvalitetenBarkdoll og Alizadeh Fard ser vand cirkulere i en eksperimentel vandtank udstyret med deres lavteknologiske, overkommelig intern rørmetode. Kredit:Michigan Technological University Dygtig, grundlæ -

En facade, der er et kraftværk og en garanti for trivselDen sydlige side af enheden SolAce med det grønblå glaserede solcelleanlæg. Kredit:Roman Keller Alle, der tilbringer det meste af deres dag indendørs, kender vigtigheden af en behagelig atmosfær

En facade, der er et kraftværk og en garanti for trivselDen sydlige side af enheden SolAce med det grønblå glaserede solcelleanlæg. Kredit:Roman Keller Alle, der tilbringer det meste af deres dag indendørs, kender vigtigheden af en behagelig atmosfær

- Rekordår for fransk champagne undlader at juble druedyrkere

- Et tre årtiers bevægende billede af unge australieres undersøgelse, arbejde, og livet

- Branson siger, at Virgin Galactic starter rumfart inden for uger

- Ny inspektionsproces fryser dele i is

- Squashing cybermobning:Ny tilgang er hurtig, nøjagtig

- Leviteret ur sætter nyt benchmark