Forskningsalliance bygger ny transistor til 5nm-teknologi

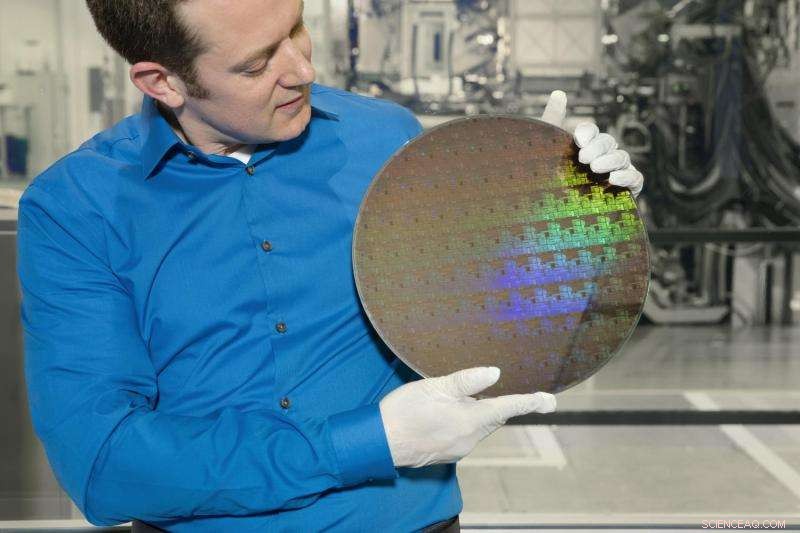

IBM Research videnskabsmand Nicolas Loubet holder en wafer af chips med 5nm silicium nanosheet transistorer fremstillet ved hjælp af en industri-første proces, der kan levere 40 procent ydeevneforbedring ved fast strøm, eller 75 procent strømbesparelse ved matchet ydeevne. Kredit:Connie Zhou

IBM, dets Research Alliance-partnere Globalfoundries og Samsung, og udstyrsleverandører har udviklet en industri-første proces til at bygge silicium nanosheet transistorer, der vil muliggøre 5 nanometer (nm) chips. Detaljerne i processen vil blive præsenteret på 2017 Symposia on VLSI Technology and Circuits konferencen i Kyoto, Japan. På mindre end to år siden udviklingen af en 7nm testknudechip med 20 milliarder transistorer, videnskabsmænd har banet vejen for 30 milliarder kontakter på en chip på størrelse med en negl.

Den resulterende stigning i ydeevne vil hjælpe med at accelerere kognitiv databehandling, tingenes internet (IoT), og andre dataintensive applikationer leveret i skyen. Strømbesparelsen kan også betyde, at batterierne i smartphones og andre mobilprodukter kan holde to til tre gange længere end nutidens enheder, før de skal oplades.

Forskere, der arbejder som en del af den IBM-ledede Research Alliance på SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex i Albany, NY opnåede gennembruddet ved at bruge stakke af silicium nanoark som enhedsstrukturen af transistoren, i stedet for standard FinFET-arkitektur, som er blueprintet for halvlederindustrien op gennem 7nm nodeteknologi.

"For at erhvervslivet og samfundet skal opfylde kravene til kognitiv og cloud computing i de kommende år, fremskridt inden for halvlederteknologi er afgørende, " sagde Arvind Krishna, senior vicepræsident, Hybrid sky, og direktør, IBM Research. "Det er derfor, IBM aggressivt forfølger nye og anderledes arkitekturer og materialer, der skubber grænserne for denne industri, og bringer dem på markedet inden for teknologier som mainframes og vores kognitive systemer."

IBM-forskere ved SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex i Albany, NY klargør testwafers med 5nm silicium nanosheettransistorer, indlæst i den forreste åbning forenet pod, eller FOUP'er, at teste en industri-første proces med at bygge 5nm transistorer ved hjælp af silicium nanosheets. Kredit:Connie Zhou

Demonstrationen af silicium nanoark transistor, som beskrevet i Research Alliance papiret Stacked Nanosheet Gate-All-Around Transistor for at muliggøre skalering ud over FinFET, og udgivet af VLSI, beviser, at 5nm chips er mulige, mere magtfuld, og ikke så langt ude i fremtiden.

Sammenlignet med den førende 10nm-teknologi, der er tilgængelig på markedet, en nanoark-baseret 5nm-teknologi kan levere 40 procent ydeevneforbedring ved fast strøm, eller 75 procent strømbesparelse ved matchet ydeevne. Denne forbedring muliggør et betydeligt løft til at opfylde de fremtidige krav til kunstig intelligens (AI) systemer, virtual reality og mobile enheder.

Opbygning af en ny switch

"Denne meddelelse er det seneste eksempel på forskning i verdensklasse, der fortsætter med at opstå fra vores banebrydende offentlig-private partnerskab i New York, " sagde Gary Patton, CTO og Head of Worldwide R&D hos Globalfoundries. "Når vi gør fremskridt i retning af at kommercialisere 7nm i 2018 på vores Fab 8-fabrik, vi forfølger aktivt næste generations teknologier ved 5nm og videre for at fastholde teknologisk lederskab og gøre det muligt for vores kunder at producere en mindre, hurtigere, og mere omkostningseffektiv generering af halvledere."

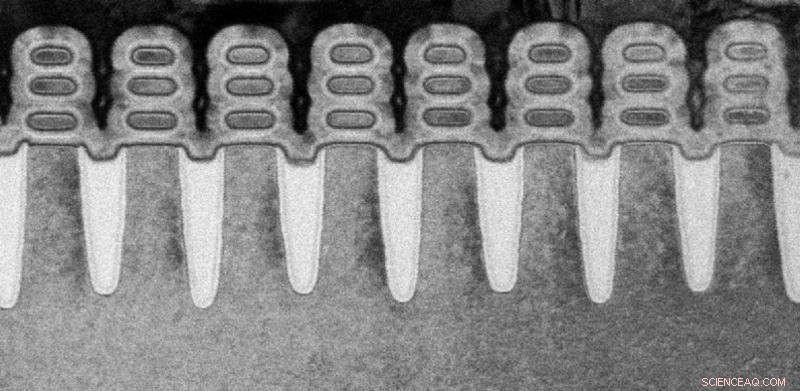

På billedet:en scanning af IBM Research Alliances 5nm transistor, bygget ved hjælp af en industri-første proces til at stable silicium nanosheets som enhedsstrukturen - for at opnå en skala på 30 milliarder switches på en fingerneglestørrelse chip, der vil levere betydelige effekt- og ydeevneforbedringer i forhold til nutidens avancerede 10nm-chips. Kredit:IBM

IBM Research har udforsket nanosheet-halvlederteknologi i mere end 10 år. Dette arbejde er det første i branchen, der demonstrerer muligheden for at designe og fremstille stablede nanoark-enheder med elektriske egenskaber, der er bedre end FinFET-arkitektur.

Den samme ekstreme ultraviolette (EUV) litografimetode, der blev brugt til at producere 7nm-testknuden og dens 20 milliarder transistorer, blev anvendt på nanoarktransistorarkitekturen. Ved hjælp af EUV litografi, bredden af nanoarkene kan justeres løbende, alt sammen inden for en enkelt fremstillingsproces eller chipdesign. Denne justerbarhed tillader finjustering af ydeevne og effekt for specifikke kredsløb – noget, der ikke er muligt med nutidens FinFET-transistorarkitekturproduktion, som er begrænset af dens strømførende finnehøjde. Derfor, mens FinFET-chips kan skaleres til 5nm, blot at reducere mængden af plads mellem finnerne giver ikke øget strømflow for yderligere ydeevne.

"Dagens meddelelse fortsætter det offentlig-private modelsamarbejde med IBM, der giver energi til SUNY-Polytechnics, Albany's, og New York State's lederskab og innovation i udviklingen af næste generations teknologier, " sagde Dr. Bahgat Sammakia, midlertidig formand, SUNY Polytekniske Institut. "Vi mener, at aktivering af den første 5nm transistor er en væsentlig milepæl for hele halvlederindustrien, da vi fortsætter med at skubbe ud over begrænsningerne af vores nuværende muligheder. SUNY Polys partnerskab med IBM og Empire State Development er et perfekt eksempel på, hvordan industri, Regeringen og den akademiske verden kan med succes samarbejde og have en bred og positiv indflydelse på samfundet."

En del af IBMs $3 mia. fem års investering i chip-F&U (annonceret i 2014), Beviset for, at nanoarkarkitektur skalering til en 5nm-node, fortsætter IBMs arv af historiske bidrag til silicium- og halvlederinnovation. De omfatter opfindelsen eller den første implementering af enkeltcellet DRAM, Dennard-skaleringslovene, kemisk forstærkede fotoresists, kobberforbindelsesledninger, Silicium på isolator, anstrengt teknik, multi-core mikroprocessorer, immersionslitografi, højhastigheds SiGe, High-k gate dielektrik, indlejret DRAM, 3-D spånstabling og luftspalte isolatorer.

Varme artikler

Varme artikler

-

Forskere bruger regnorme til at skabe kvanteprikkerSkema af den anvendte regnorm og optisk karakterisering af kvanteprikkerne. Kredit:(c) Natur nanoteknologi 8, 57–60 (2013) doi:10.1038/nnano.2012.232 (Phys.org)—Det er lykkedes britiske forskere

Forskere bruger regnorme til at skabe kvanteprikkerSkema af den anvendte regnorm og optisk karakterisering af kvanteprikkerne. Kredit:(c) Natur nanoteknologi 8, 57–60 (2013) doi:10.1038/nnano.2012.232 (Phys.org)—Det er lykkedes britiske forskere -

Den perfekte sigte i atomskalaProtontransport gennem 2D-krystaller studeret ved hjælp af vandige opløsninger. -en Eksempler på jeg – V egenskaber for 1 M HCl. Indsats nederst:zoom ind. Topindsats:elektronmikrofotografi af en

Den perfekte sigte i atomskalaProtontransport gennem 2D-krystaller studeret ved hjælp af vandige opløsninger. -en Eksempler på jeg – V egenskaber for 1 M HCl. Indsats nederst:zoom ind. Topindsats:elektronmikrofotografi af en -

Fra massive supercomputere kommer de mindste transistorerVisualiseringer af fremtidige nanotransistorer, med uret starter øverst til venstre:a) Billedet viser atomernes organisering i en Ultra Thin Body (UTB) transistor og mængden af elektrisk potentiale

Fra massive supercomputere kommer de mindste transistorerVisualiseringer af fremtidige nanotransistorer, med uret starter øverst til venstre:a) Billedet viser atomernes organisering i en Ultra Thin Body (UTB) transistor og mængden af elektrisk potentiale -

Ny teknik tillader nanobiopsier af levende celler(Phys.org) – Forskere ved UC Santa Cruz har udviklet et robot-nanobiopsi-system, der kan udtrække bittesmå prøver inde fra en levende celle uden at dræbe den. Enkeltcellet nanobiopsi-teknikken er et k

Ny teknik tillader nanobiopsier af levende celler(Phys.org) – Forskere ved UC Santa Cruz har udviklet et robot-nanobiopsi-system, der kan udtrække bittesmå prøver inde fra en levende celle uden at dræbe den. Enkeltcellet nanobiopsi-teknikken er et k

- Manglende tilpasning til klimaændringer vil sandsynligvis koste mindst fem gange mere

- Sådan konverteres damptryk til koncentration

- Forskere måler en rekordhøj koncentration af mikroplast i arktisk havis

- Vulkan på Bali bryder ud, kortvarig afbrydelse af flyrejser (opdatering)

- Integrering af satellit- og socioøkonomiske data for at forbedre klimaændringspolitikken

- Skorpebevægelser og belastningshastigheder i den sydlige Basin and Range-provins