Fremmer fremtiden:Det mindste helt digitale kredsløb åbner døre til 5 nm næste generations halvleder

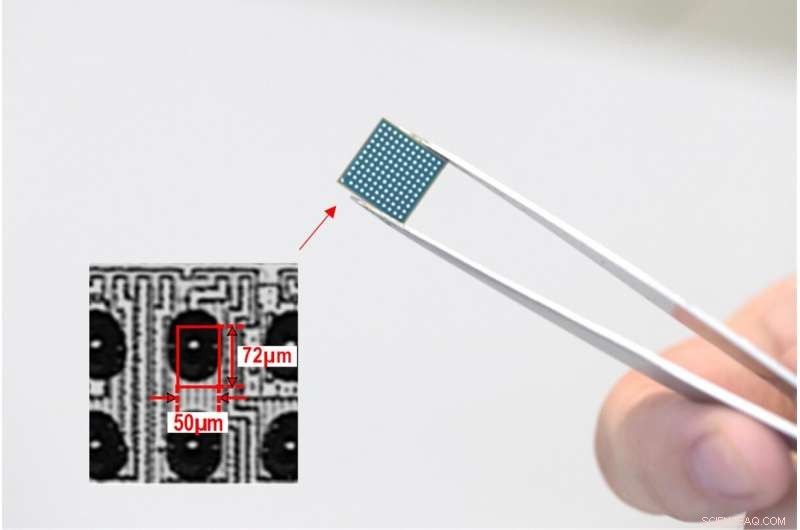

Hele den helt digitale PLL passer i en 50 × 72 μm2 region, hvilket gør det til den mindste PLL til dato. Kredit:Kenichi Okada

Forskere ved Tokyo Institute of Technology (Tokyo Tech) og Socionext Inc. har designet verdens mindste helt digitale faselåste loop (PLL). PLL'er er kritiske urkredsløb i stort set alle digitale applikationer, og at reducere deres størrelse og forbedre deres ydeevne er et nødvendigt skridt for at muliggøre udvikling af næste generations teknologier.

Nye eller forbedrede teknologier, såsom kunstig intelligens, 5G mobilkommunikation, og tingenes internet, forventes at bringe revolutionære ændringer i samfundet. Men for at det kan ske, højtydende system-on-a-chip (SoC)-en type integreret kredsløb-enheder er uundværlige. En kerne-byggesten i SoC-enheder er den faselåste sløjfe (PLL), et kredsløb, der synkroniserer med frekvensen af en referencesvingning og udsender et signal med samme eller højere frekvens. PLL'er genererer 'klokkesignaler, 'hvis svingninger fungerer som en metronom, der giver en præcis tidsreference for harmonisk drift af digitale enheder.

For at SoC -enheder med høj ydeevne skal realiseres, fremstillingsprocesser for halvlederelektronik skal blive mere sofistikerede. Jo mindre området til implementering af digitale kredsløb er, jo bedre ydelse af enheden. Producenter har kapperet om at udvikle stadig mindre halvledere. 7 nm halvledere (en massiv forbedring i forhold til deres forgænger på 10 nm) er allerede i produktion, og metoder til at bygge 5 nm dem bliver nu set på.

Imidlertid, i denne bestræbelse står en stor flaskehals. Eksisterende PLL'er kræver analoge komponenter, som generelt er omfangsrige og har designs, der er svære at nedskalere.

Forskere ved Tokyo Tech og Socionext Inc., ledet af prof. Kenichi Okada, har løst dette problem ved at implementere en 'syntetiserbar' fraktioneret-N PLL, som kun kræver digitale logikporte, og ingen omfangsrige analoge komponenter, gør det let at anvende i konventionelle miniaturiserede integrerede kredsløb.

Okada og team brugte flere teknikker til at reducere det nødvendige område, strømforbrug og jitter - uønskede tidssvingninger ved transmission af digitale signaler - af deres syntetiserbare PLL'er. For at reducere areal, de brugte en ringoscillator, en kompakt oscillator, der let kan skaleres ned. For at undertrykke jitter, de reducerede fasestøj - tilfældige udsving i et signal - fra denne ringoscillator, ved hjælp af 'injektionslås' - processen med at synkronisere en oscillator med et eksternt signal, hvis frekvens (eller flere af den) er tæt på oscillatorens - over en lang række frekvenser. Den lavere fase støj, på tur, reduceret strømforbrug.

Designet af denne syntetiserbare PLL slår alle andre aktuelle topmoderne PLL'er i mange vigtige aspekter. Det opnår den bedste jitterydelse med det laveste strømforbrug og det mindste område (som det kan ses i figur 1). "Kerneområdet er 0,0036 mm2, og hele PLL'en implementeres som et layout med en enkelt strømforsyning, "bemærker Okada. Yderligere, det kan bygges ved hjælp af standard digitale designværktøjer, muliggøre dens hurtige, lav indsats, og billig produktion, gør det kommercielt levedygtigt.

Denne syntetiserbare PLL kan let integreres i designet af helt digitale SoC'er, og er kommercielt levedygtig, gør det værdifuldt til udvikling af den meget eftertragtede 5 nm halvleder til banebrydende applikationer, herunder kunstig intelligens, tingenes internet og mange andre, hvor høj ydelse og lavt strømforbrug ville være de kritiske krav. Men bidragene fra denne forskning går ud over disse muligheder. "Vores arbejde demonstrerer potentialet i syntetiserbare kredsløb. Med designmetoden anvendt her, andre byggesten i SoC'er, såsom datakonvertere, strømstyringskredsløb, og trådløse transceivere, kunne også gøres syntetisk. Dette vil i høj grad øge designproduktiviteten og reducere designindsatsen betydeligt, "forklarer Okada. Tokyo Tech og Socionext vil fortsætte deres samarbejde i dette arkiv for at fremme miniaturiseringen af elektroniske enheder, muliggør realisering af nyere generationsteknologier.

Varme artikler

Varme artikler

-

Lav værktøjerne til at forbinde isiXhosa og isiZulu med den digitale tidsalderSoftwareværktøjer kan tage flere sprog til helt nye rum. Kredit:Zubada/Shutterstock Vi lever i en verden, hvor der tales omkring 7000 sprog, og en, hvor informations- og kommunikationsteknologier

Lav værktøjerne til at forbinde isiXhosa og isiZulu med den digitale tidsalderSoftwareværktøjer kan tage flere sprog til helt nye rum. Kredit:Zubada/Shutterstock Vi lever i en verden, hvor der tales omkring 7000 sprog, og en, hvor informations- og kommunikationsteknologier -

Overvejer du at forlade Facebook? Det er der en demografisk analyse forFolk er enten Facebook-brugere, eller også er de ikke. Facebook-brugerdata kan bruges til at drage konklusioner om generelle sociale fænomener. Ifølge Eric P.S. Baumer, der studerer menneske-comput

Overvejer du at forlade Facebook? Det er der en demografisk analyse forFolk er enten Facebook-brugere, eller også er de ikke. Facebook-brugerdata kan bruges til at drage konklusioner om generelle sociale fænomener. Ifølge Eric P.S. Baumer, der studerer menneske-comput -

Matematisk verifikation tester, om softwaren kører som annonceretKredit:CC0 Public Domain Når det kommer til sikkerhed, hvad du ikke ved kan skade dig. De fleste mennesker tænker aldrig på den kryptering, der ligger til grund for sikre onlineaktiviteter, herun

Matematisk verifikation tester, om softwaren kører som annonceretKredit:CC0 Public Domain Når det kommer til sikkerhed, hvad du ikke ved kan skade dig. De fleste mennesker tænker aldrig på den kryptering, der ligger til grund for sikre onlineaktiviteter, herun -

Ultralet videnskab-målinger af grænselag fra lavflyvende kildeUW Atmosfærisk og Oceanisk Videnskab Professor Grant Petty tager Zigolo MG12 ultralette fly til den første testflyvning 30. oktober, 2017. Kredit:Jonathan Thom På en græsklædte landingsbane lige u

Ultralet videnskab-målinger af grænselag fra lavflyvende kildeUW Atmosfærisk og Oceanisk Videnskab Professor Grant Petty tager Zigolo MG12 ultralette fly til den første testflyvning 30. oktober, 2017. Kredit:Jonathan Thom På en græsklædte landingsbane lige u

- Det tager en DJ:Sunde revlyde kan lokke fisk til beskadigede rev

- Forskere:Vinde, der er pisket af klimaet, udgør en fare for Great Lakes

- Sådan beregnes område fra bredde og længde

- Evakueringer begynder i Bahamas, da kategori 4 Dorian holder ned

- Surfing i et lysvågning:Forskere observerer og kontrollerer lysvågninger for første gang

- Hvilke farver afspejler mere lys?