Universal transistor tjener som grundlag for at udføre enhver logisk funktion

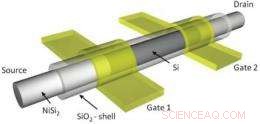

Den rekonfigurerbare transistors kerne består af en nanotrådstruktur indlejret i en siliciumdioxidskal. Elektroner eller huller strømmer fra kilden i den ene ende af nanotråden gennem to porte til afløbet i den anden ende af nanotråden. En gate bruges til at programmere p- eller n-polariteten, hvorimod den anden gate indstiller konduktansen gennem nanotråden. Billedkredit:©Namlab gGmbH

(PhysOrg.com) - De fleste af nutidens elektroniske enheder indeholder to forskellige typer felteffekttransistorer (FET'er):n-type (som bruger elektroner som ladningsbærer) og p-type (som bruger huller). Generelt, en transistor kan kun være den ene eller den anden type, men ikke begge dele. Nu i en ny undersøgelse, forskere har designet en transistor, der kan rekonfigurere sig selv som enten n-type eller p-type, når den programmeres af et elektrisk signal. Et sæt af disse "universelle transistorer" kan, i princippet, udføre enhver boolsk logisk operation, hvilket betyder, at kredsløb kunne udføre det samme antal logiske funktioner med færre transistorer. Denne fordel kunne føre til mere kompakt hardware og nye kredsløbsdesign.

Forskerne, der designede transistoren, ledet af Walter M. Weber ved Namlab gGmbH i Dresden, Tyskland, har offentliggjort det nye koncept i et nyligt nummer af Nano bogstaver .

"Syntetiske nanotråde bruges til at realisere proof-of-princippet, ” fortalte Weber PhysOrg.com . "Imidlertid, konceptet er fuldt overførbart til state-of-the-art CMOS silicium teknologi og kan gøre brug af selvjusterede processer."

Den nye transistors kerne består af en enkelt nanotråd lavet af en metal-halvleder-metal struktur, som er indlejret i en siliciumdioxidskal. Elektroner eller huller strømmer fra kilden i den ene ende af nanotråden gennem to porte til afløbet i den anden ende af nanotråden. De to porte styrer strømmen af elektroner eller huller på forskellige måder. En gate vælger transistortypen ved at vælge at bruge enten elektroner eller huller, mens den anden gate styrer elektronerne eller hullerne ved at indstille nanotrådens ledningsevne.

Brug af en gate til at vælge p- eller n-type konfiguration er helt anderledes end konventionelle transistorer. I konventionelle transistorer, p- eller n-type operation er resultatet af doping, der forekommer under fremstillingsprocessen, og kan ikke ændres, når først transistoren er lavet. I modsætning, den rekonfigurerbare transistor bruger ingen doping. I stedet, en ekstern spænding påført en gate kan rekonfigurere transistortypen selv under drift. Spændingen får Schottky-krydset nær porten til at blokere enten elektroner eller huller i at strømme gennem enheden. Så hvis elektroner er blokeret, huller kan flyde og transistoren er p-type. Ved at anvende en lidt anden spænding, omkonfigurationen kan skiftes igen, uden at forstyrre flowet.

Forskerne forklarer, at nøglen til at få denne omkonfiguration til at fungere er evnen til at indstille den elektroniske transport på tværs af hver af de to vejkryds (én pr. gate) separat. Deres simuleringer viste, at strømmen er domineret af tunnelering, tyder på, at nanotrådsgeometrien spiller en vigtig rolle i evnen til uafhængig junction-kontrol.

Fordi den rekonfigurerbare transistor kan udføre de logiske funktioner af både p- og n-type FET'er, en enkelt transistor kunne erstatte både en p- og n-type FET i et kredsløb, hvilket ville reducere størrelsen af kredsløbet betydeligt uden at reducere funktionaliteten. Selv på dette tidlige stadie, den rekonfigurerbare transistor viser meget gode elektriske egenskaber, inklusive et rekordstort tænd/sluk-forhold og reduceret lækstrøm sammenlignet med konventionelle nanotråd-FET'er. I fremtiden, forskerne planlægger at forbedre transistorens ydeevne yderligere.

"Vi varierer materialekombinationerne for yderligere at øge enhedens ydeevne, sagde Weber. "Længere fremme, de første kredsløb, der implementerer disse enheder, er ved at blive bygget. … Den største udfordring bliver at inkorporere de ekstra gate-signaler i cellelayoutet, hvilket muliggør fleksibel sammenkobling til de andre transistorer."

Copyright 2011 PhysOrg.com.

Alle rettigheder forbeholdes. Dette materiale må ikke offentliggøres, udsende, omskrevet eller omdistribueret helt eller delvist uden udtrykkelig skriftlig tilladelse fra PhysOrg.com.

Varme artikler

Varme artikler

-

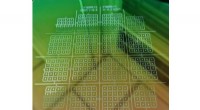

Forskning:Grafen vokser bedre på visse kobberkrystallerEn illustration af gengivne eksperimentelle data, der viser den polykrystallinske kobberoverflade og de forskellige grafendækninger. Grafen vokser i et enkelt lag på (111) kobberoverfladen og på øer o

Forskning:Grafen vokser bedre på visse kobberkrystallerEn illustration af gengivne eksperimentelle data, der viser den polykrystallinske kobberoverflade og de forskellige grafendækninger. Grafen vokser i et enkelt lag på (111) kobberoverfladen og på øer o -

Forskere tænker små for at gøre fremskridt mod bedre brændselscellerKandidatstuderende Jennifer Lee bruger et stort transmissionselektronmikroskop, til huse i Singh Center, for at se nærmere på de nanomaterialer og nanokrystaller, der syntetiseres i laboratoriet. Kred

Forskere tænker små for at gøre fremskridt mod bedre brændselscellerKandidatstuderende Jennifer Lee bruger et stort transmissionselektronmikroskop, til huse i Singh Center, for at se nærmere på de nanomaterialer og nanokrystaller, der syntetiseres i laboratoriet. Kred -

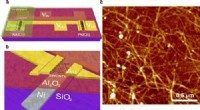

Carbon nanorør -logisk enhed fungerer på subnanowatt -strømIllustrationer af (a) CNT CMOS-inverteren og (b) et tværsnit af en individuel CNT-transistor, inklusive en 25 nm tyk Ni-port, der muliggør ultralavt strømforbrug. (c) Atomkraftmikroskopibillede af CNT

Carbon nanorør -logisk enhed fungerer på subnanowatt -strømIllustrationer af (a) CNT CMOS-inverteren og (b) et tværsnit af en individuel CNT-transistor, inklusive en 25 nm tyk Ni-port, der muliggør ultralavt strømforbrug. (c) Atomkraftmikroskopibillede af CNT -

Udvikling af bedre nanopore-teknologiOprettelse af ultratynde membraner til CBD-enheder. Kredit:James Yates På det enkleste niveau, nanoporer er (nanometer-størrelse) huller i en isolerende membran. Hullet tillader ioner at passere g

Udvikling af bedre nanopore-teknologiOprettelse af ultratynde membraner til CBD-enheder. Kredit:James Yates På det enkleste niveau, nanoporer er (nanometer-størrelse) huller i en isolerende membran. Hullet tillader ioner at passere g

- Fornax En galakse undersøgt med AstroSat

- NASAs Lucy-mission:En rejse til det unge solsystem

- Ud over qubits:Team tager det næste store skridt for at opskalere kvanteberegning

- Tre eksempler på simple destillationsblandinger

- Sådan beregnes spændingen i en Rope

- Mikroplastikforurening fundet i almindelig grundvandskilde, rapporterer forskere