Samsung til støberi-event taler om 3nm, MBCFET udvikling

Kredit:Samsung

"Nanometerprocessen omhandler rummet mellem transistorerne monteret på et substrat på nanometerniveau, " sagde Puls .

"Jo smallere afstanden er, jo flere chips kan presses ind for at øge computerkraften og energieffektiviteten. En nanometer svarer til en ti tusindedel af diameteren af et menneskehår."

På Samsung Foundry Forum i Santa Clara, Californien, virksomheden forsøgte for nylig at imponere fremskridt, det har gjort inden for 3nm gate-all-around (GAA) procesudvikling.

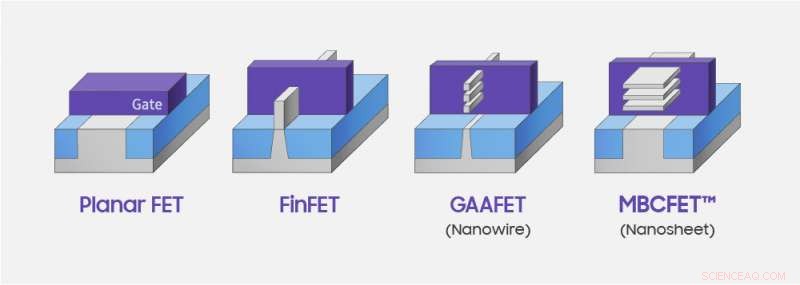

Samsung Foundry introducerer nu MBCFET (multi bridge channel FET). Dette består af multi-stablede nanoark. Med dannelsen af nanoark, en større strøm pr. stak er opnåelig, sagde SamMobile .

ExtremeTech beskrev meddelelsen som værende om "en ny, udviklet transistorarkitektur" der kommer ud af Samsung Foundry - der involverer "nanosheets"-tilgangen for dets 3nm-node.

(Fra Samsungs nyhedsredaktion:"Konventionel GAA baseret på nanowire kræver et større antal stakke på grund af dens lille effektive kanalbredde. På den anden side, Samsungs patenterede version af GAA, MBCFET (Multi-Bridge-Channel FET), bruger en nanoark-arkitektur, muliggør større strøm pr. stak.")

Bloggen CNXSoft kastede yderligere lys over hvorfor overgangen fra nanotråde til nanoark.

"Vi læser ofte, at nye processorer er fremstillet med en FinFET-proces. Den nye proces blev skabt på grund af korte kanaleffekter i traditionelle plane transistorer, og FinFET (Fin Field-effect transistor) blev introduceret for at muliggøre yderligere spændingsskalering, men med procesknudepunktet, der blev mindre og mindre, elektrostatiske effekter begyndte at forårsage problemer."

Brug af GAA (Gate All Around) nanotråde til at begrænse disse effekter blev taget som et svar, men de er tilsyneladende virkelig svære at integrere i silicium, sagde bloggen, så Samsung endte med at bruge tynde lag (nanoark) i stedet for nanotråde, "aktiverer større strøm pr. spor i deres GAA-implementering kaldet MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

For dem, der har brug for at behandle overbelastningen af akronymer, Ramish Zafar ind Wccftech tog sine læsere med på Samsung-rejsen. 1. Samsung samarbejdede med IBM om GAAFET-procesknuder (Gate-All-Around). 2. Nu har virksomheden annonceret sine tilpasninger til den tidligere proces, og dette er MBCFET.

Zafar havde mere at sige om MBCET. "I modsætning til traditionelle FinFET-designs, GAAFET tillader portmaterialet at omgive kanalen fra alle sider. Samsung hævder, at MBCFETs design vil forbedre processens on-off adfærd, og tillade processorer at reducere driftsspændingen under 0,75V. Et afgørende punkt for MBCFET er, at processen er fuldt ud kompatibel med FinFET-design og ikke kræver nye værktøjer til fremstilling."

Kredit:Samsung

Hvordan, selvom, indgår alle disse gode nyheder i virksomhedens udviklingsplaner. Hvornår kan vi forvente at se teknologi i aktion? Joel Hruska adresserede dette i ExtremeTech .

"På deres Samsung Foundry Forum i denne uge, Samsung erklærede, at dets produktdesignsæt til 3nm-chips nu er i alfa, efter at have nået udviklingsmilepælen på 0,1. Samsung planlægger at lancere et væld af procesknuder i de kommende år, med udviklingsspor planlagt til 7nm, 6nm, 5nm, 4nm, og ja, 3nm."

Hruska tilføjede, "Forbedringerne for 3nm sammenlignet med 7nm er ret gode, men denne node vil faktisk ikke blive sendt i et stykke tid." Hans artikel indeholder et diagram, der viser progressionen som kommunikeret af Samsung.

© 2019 Science X Network

Varme artikler

Varme artikler

-

Bilproducenter opfordrer Californien, USA genstarter forhandlinger om kilometertalI denne 10. dec. 2015, fil foto, køretøjer kører vestpå ad Interstate 80 over San Francisco-Oakland Bay Bridge set fra Treasure Island i San Francisco. Store bilproducenter opfordrer Trump-administrat

Bilproducenter opfordrer Californien, USA genstarter forhandlinger om kilometertalI denne 10. dec. 2015, fil foto, køretøjer kører vestpå ad Interstate 80 over San Francisco-Oakland Bay Bridge set fra Treasure Island i San Francisco. Store bilproducenter opfordrer Trump-administrat -

Kanariefugle i kulminen:Singapore-veer ringer handelsalarmklokkerSingapore er meget afhængig af handel og har traditionelt været et af de første steder i Asien, der er blevet ramt under globale nedgangstider - med krusninger, der typisk breder sig ud over regionen

Kanariefugle i kulminen:Singapore-veer ringer handelsalarmklokkerSingapore er meget afhængig af handel og har traditionelt været et af de første steder i Asien, der er blevet ramt under globale nedgangstider - med krusninger, der typisk breder sig ud over regionen -

Fleksibel ultralydsplaster kan gøre det lettere at inspicere skader i ulige formede strukturerDenne strækbare, fleksibel ultralydsplaster kan gøre det lettere at inspicere skader dybt inde i ulige formede strukturer, såsom motordele, møller, reaktorrørbuer og jernbanespor-objekter, der er vans

Fleksibel ultralydsplaster kan gøre det lettere at inspicere skader i ulige formede strukturerDenne strækbare, fleksibel ultralydsplaster kan gøre det lettere at inspicere skader dybt inde i ulige formede strukturer, såsom motordele, møller, reaktorrørbuer og jernbanespor-objekter, der er vans -

Smarte bygninger står over for udfordringer, men har masser af potentialeMohamed Ouf:Okkupant-centreret kontrol giver spændende muligheder. Kredit:Concordia University Vi hører ofte ordet smart anvendt på dagligdags genstande:smartphones, smart tv, smarte apparater - o

Smarte bygninger står over for udfordringer, men har masser af potentialeMohamed Ouf:Okkupant-centreret kontrol giver spændende muligheder. Kredit:Concordia University Vi hører ofte ordet smart anvendt på dagligdags genstande:smartphones, smart tv, smarte apparater - o

- Sådan forstår du talesæt <p> Et sæt er en hvilken som helst gruppe af objekter. I matematik in…

- Folks motivation påvirker, hvordan de indsamler information

- Baby boomere eller millennials? Fire generationer er i dagens arbejdsstyrke

- Hvordan virker parfumeatomeren?

- Hvad er de fire kvadranter på en graf?

- Det største virtuelle univers nogensinde simuleret