Ny standard tillader stablede matricer i 3-D integrerede kredsløb at forbinde med testudstyr

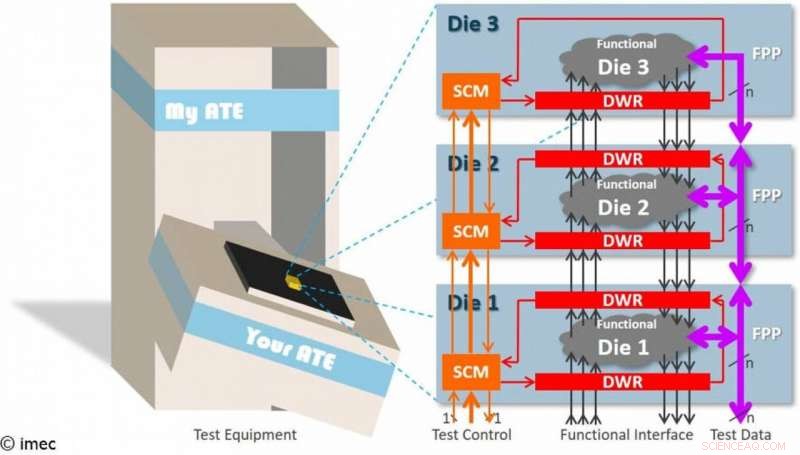

Konceptuelt tværsnit af en 3D-IC bestående af tre stablede matricer. Testudstyr sender teststimuli ind i og modtager testsvar fra 3D-IC’ens eksterne grænseflade placeret i bunden af stakken. IEEE Std 1838™-2019 design-for-test-elementerne i de forskellige dyser danner en konsistent testadgangsarkitektur, hvorigennem testudstyret kan få adgang til hver die i stakken. Kredit:IMEC

Denne uge, IMEC, et verdensførende forsknings- og innovationsknudepunkt inden for nanoelektronik og digitale teknologier, annonceret, at IEEE Std 1838TM-2019 – for nylig godkendt af IEEE Standards Association – vil blive inkluderet i IEEE Xplore Digital Library fra februar 2020 og frem. Den nye standard gør det muligt for matriceproducenter at designe matricer, som hvis den er i overensstemmelse med denne standard, udgøre, en gang stablet i en 3-D-IC af en stakintegrator, en konsekvent testadgangsarkitektur på stakniveau. Standardiseringsindsatsen for 3-D-DfT (design-for-test) blev initieret af IMEC.

3-D-IC'er udnytter den vertikale dimension til yderligere integration ved at stable matricer oven på hinanden som en måde at holde momentum af Moores lov i gang. Eric Beyne, fellow og program director 3-D System Integration hos IMEC, siger, "Fremskridt inden for wafer-bearbejdning og stack-samlingsteknologier skaber et væld af forskellige stack-arkitekturer. Dette forårsager en kraftig stigning i antallet af potentielle øjeblikke, hvor testning for produktionsfejl kan udføres:pre-bond (før stacking), mid-bond (på delvis stakke), post-bond (på komplette stakke), og afsluttende test (på emballerede 3-D-IC'er). Testudstyr kontakter IC'er via dets eksterne interface gennem sondenåle eller ved teststik. I en matricestabel, den eksterne grænseflade ligger typisk i stakkens bundmatrice. For at testudstyret skal kunne levere teststimuli til og modtage svar fra de forskellige dies oppe i stakken, samarbejde fra de underliggende matricer er påkrævet for at give testadgang til den matrice, der i øjeblikket testes."

En IEEE-arbejdsgruppe til standardisering af 3-D-DfT blev grundlagt i 2011 af Erik Jan Marinissen, videnskabelig direktør ved IMEC i Leuven, Belgien, og han fungerede som dens første formand. I de seneste år, Adam Cron, ledende R&D-ingeniør i Designgruppen hos Synopsys, har været drivkraften som nuværende formand for Arbejdsgruppen.

Amit Sanghani, vicepræsident for engineering i Design Group hos Synopsys i Mountain View, Californien, U.S. udtalte:"3-D-IC er en vigtig teknologi til at levere den næste bølge af innovation, når industrien skalerer forbi 7nm. I øjeblikket, matricen kan komme fra forskellige leverandører med usammenhængende DfT-arkitekturer.

Den nye standard består af tre hovedelementer. (1) DWR, matriceindpakningsregistret:scan kæder ved grænsen af hver matrice i stakken for at muliggøre modulær test af det indre af hver matrice og af forbindelserne mellem hvert par af tilstødende matricer. (2) SCM, den serielle kontrolmekanisme:en enkelt-bit testkontrolmekanisme, der transporterer instruktioner ind i stakken for at kontrollere testtilstandene for de forskellige dyseindpakninger. (3) FPP, den valgfri fleksible parallelport, dvs. en skalerbar multi-bit testadgangsmekanisme til effektivt at transportere de store datamængder, der typisk er forbundet med produktionstest, op og ned i matricestakken. Mens DWR og SCM er baseret på eksisterende DfT-standarder, FPP er virkelig ny for IEEE Std 1838.

Wolfgang Meyer, senior gruppedirektør R&D hos Cadence Design Systems i San Jose, Californien, OS., siger, "En DfT-standard som IEEE Std 1838 er vigtig for industrien. Matriceproducenter ved, hvad de skal levere, og stakintegratorer ved, hvad de kan forvente. I øvrigt, EDA-leverandører som Cadence kan fokusere deres værktøjssupport på arkitekturer, der er i overensstemmelse med den nye standard. Det er godt, at der er en vis brugerdefineret skalerbarhed med standarden, da 3-D-IC-feltet er så bredt - en rigid 'one-size-fits-all'-standard ville ikke fungere."

Junlin Huang, leder af et 150 mand stærkt DfT-team af HiSilicon i Shenzhen, Kina, siger, "Per år, vi udfører DfT-indsættelse og automatisk testmønstergenerering (ATPG) til titusvis af meget store og komplekse digitale chipdesign i de mest avancerede teknologier. Nu, disse produkter begynder at bruge 3-D-teknologi, og mit DfT-team skal være klar til at håndtere de tilhørende DfT- og ATPG-udfordringer. IEEE Std 1838 vil hjælpe os med den opgave."

Fra februar 2020 og frem den nye standard IEEE Std 1838 vil være tilgængelig via IEEE Xplore for abonnenter af IEEE-standarder såvel som til køb til alle andre.

Varme artikler

Varme artikler

-

Visa tæt på normalt efter udfald blokerer transaktioner i hele Europa (Opdatering)Visa-brugere tog til sociale medier for at klage over problemer med at behandle transaktioner i Europa Betalingssystemgiganten Visa sagde sent fredag, at den fungerer tæt på normale niveauer, efte

Visa tæt på normalt efter udfald blokerer transaktioner i hele Europa (Opdatering)Visa-brugere tog til sociale medier for at klage over problemer med at behandle transaktioner i Europa Betalingssystemgiganten Visa sagde sent fredag, at den fungerer tæt på normale niveauer, efte -

Magt-sultede Etiopien stævner omkring Nildæmningen, da Egypten strider mod hinandenGrand Ethiopian Renaissance Dam bliver det største vandkraftværk i Afrika Mobiltelefonbatterier dør konstant, sundhedscentre uden moderne udstyr, en afhængighed af lommelygter efter solnedgang - K

Magt-sultede Etiopien stævner omkring Nildæmningen, da Egypten strider mod hinandenGrand Ethiopian Renaissance Dam bliver det største vandkraftværk i Afrika Mobiltelefonbatterier dør konstant, sundhedscentre uden moderne udstyr, en afhængighed af lommelygter efter solnedgang - K -

De sociale dyr, der inspirerer til ny adfærd for robotsværmeTermithold. Kredit:7. Son Studio/Shutterstock Fra fugleflokke til fiskeskoler i havet, eller tårnhøje termithøje, mange sociale grupper i naturen eksisterer sammen for at overleve og trives. Denne

De sociale dyr, der inspirerer til ny adfærd for robotsværmeTermithold. Kredit:7. Son Studio/Shutterstock Fra fugleflokke til fiskeskoler i havet, eller tårnhøje termithøje, mange sociale grupper i naturen eksisterer sammen for at overleve og trives. Denne -

Studerende sigtet for en omfattende digital pengetyveriordningI denne 31. maj, 2016 foto, Joel Ortiz, centrum, poserer til et billede med borgmester Marty Walsh, venstre, og offentlige skoler Superintendent Tommy Chang, ret, under en frokost for offentlige skole

Studerende sigtet for en omfattende digital pengetyveriordningI denne 31. maj, 2016 foto, Joel Ortiz, centrum, poserer til et billede med borgmester Marty Walsh, venstre, og offentlige skoler Superintendent Tommy Chang, ret, under en frokost for offentlige skole

- Plastens verden, i tal

- Forskere løser, hvordan svampe producerer forbindelser med potentielle farmaceutiske anvendelser

- Campus naturgas kraftværker udgør ingen radonrisici

- Undersøgelse:Stigning i cannabisdyrkning eller boligudvikling kan påvirke vandressourcerne

- Nyt værktøj kunne behandle blodinfektioner hurtigt

- NASA -rumfartøjer slår rekord for at komme tættest på Solen